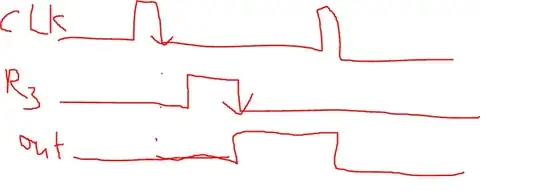

Please look at the picture for this description. I have a problem with writing verilog for the following logic: Consider clk and R3 are input signals & out is the output signal. At the falling edge of clk, out is reset to 0. At the falling edge of R3, out is set to 1. How can I implement this logic in verilog? I am stuck because it seems to me that there is no way to distinguish between falling edge of R3 and falling edge of clk.

At the falling edge of both clk and R3, both clk and R3 are equal to 0 so I can't distinguish them.

module startup(clk, R3, out);

input clk, R3;

output reg out;

always@(negedge clk, negedge R3) begin

end

endmodule