You don't want to have two different always blocks controlling one signal.

Here's my version to avoid that

always @(negedge s1 or posedge clk) begin

if(clk)

saw_a_falling_edge <= 1'b0;

else

saw_a_falling_edge <= 1'b1;

end

always @(posedge clk) begin

out <= saw_a_falling_edge;

end

This is inferring a DFF with asynchronous clear to drive saw_a_falling_edge. The clk signal is connected to the CLEAR input and the s1 signal is connected to the clock. The D input is tied high.

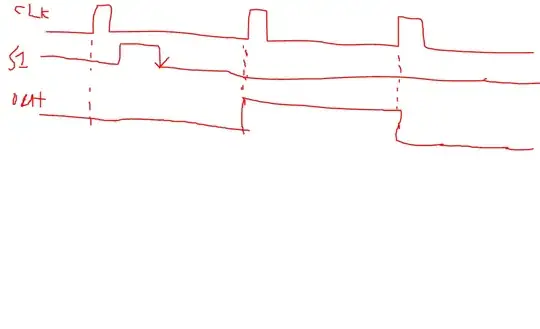

If you did it the other way around then if the clock edge happened while s1 was still low, the output wouldn't go high (violating the requested behavior per your timing diagram).

Be aware the above solution won't handle the case that s1 goes low while clk remains high. It's not clear to me from your problem statement whether you need to handle that or not.