I would like to ask how to set a particular layout during transpiling. I guess that the layout can be set by the initial_layout parameter in the transpiler. However, there are several options that may conflict, namely: layout_method, and optimisation optimization_level. I do not know which one suppress the other. I guess that optimization_level setting to 0 can enforce it. But on the other hand I still want to a bit of optimising anything else apart from the layout. I search out for the documentation but there seems to be not much talking about this. Any help is very appreciated.

- 8,429

- 3

- 11

- 39

- 81

- 1

1 Answers

Disclaimer: I might be plain wrong:) More experienced qiskit users/developers are encouraged comment!

I guess initially I was thinking about layouts the way are thinking right now. I assumed that the choice of initial_layout binds the logical qubits from my original circuit to the physical qubits and this binding remains intact during the computation. However, a better way to think about this is that logical qubits are constantly moving around. Although you should be able to say at each moment which physical qubit stores a given logical qubit this mapping can change dynamically. Moreover, it may be not possible to keep it constant because of the connectivity constraints or even if it is possible, it might not be efficient.

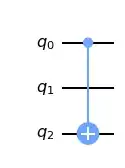

Let us consider a simple example, a CNOT gate

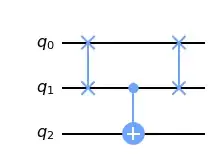

Assume that you can only apply two-quit gates between $q_0,q_1$ and $q_1,q_2$. Then this circuit could be made compatible with this connectivity by adding some SWAPs

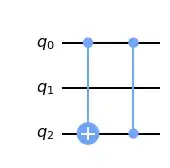

Even if in the initial layout your control qubit was mapped to $q_0$ after the first SWAP it sits at $q_1$. Yes, we can then perform our CNOT and return the state of the control qubit back to $q_0$ (by the second SWAP, as shown on the image), but this might not be efficient. Suppose that you want to make two gates between $q_0$ and $q_2$, like here

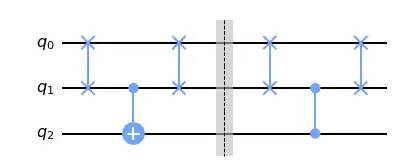

If you insist that your initial layout be restored after each logical gate you can do it as follows (at the barrier the initial layout is restored)

However, this is obviously inefficient as the two subsequent SWAPs combine to an identity.

OK, so qiskit has a lot of clever algorithms to avoid this kind inefficiency and thy involve frequent rearrangements of logical qubits. Initial layout simply determines how do you start. If you still insist on keeping the layout fixed you should probably explain why and, in the case of constrained connectivity, in what sense?

p.s. A gotcha. Precisely because of the reasons I described qiskit's transpiler does not attempt to restore the initial layout at the end of the transpilation. If you measure your state in the end, it just maps the physical qubits to the classical registers according to the last layout. However, at some point I was interested in the unitary matrix of the circuit Transpilation on restricted topology does not yield an equivalent circuit in Qiskit , and without measurements I did not find a way to figure out the final layout. So in this sense the transpilation of a circuit does not always preserve the unitary matrix of the circuit.

- 1,725

- 6

- 22