I would like to better understand this topic: Minimum ON time for a buck converter

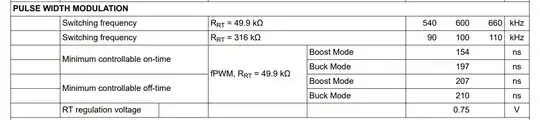

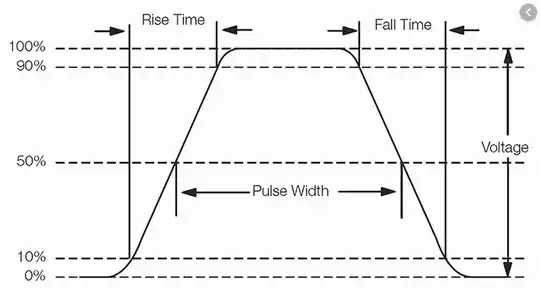

One of the answers seems to say that the minimum on-time depends on the selected MOSFET. According to the datasheet that I can find on internet, there is no information about the minimum on time. Here is an example :

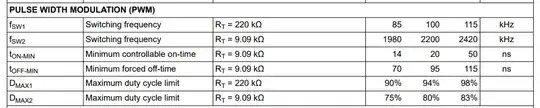

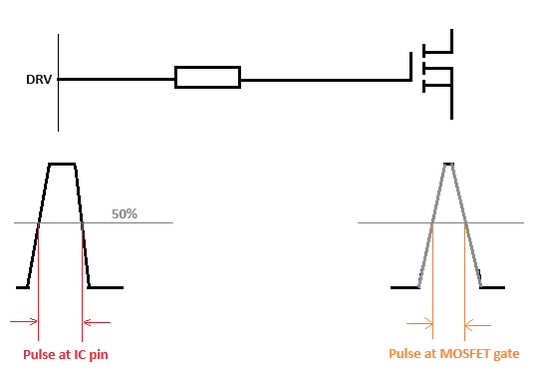

Here is another example :

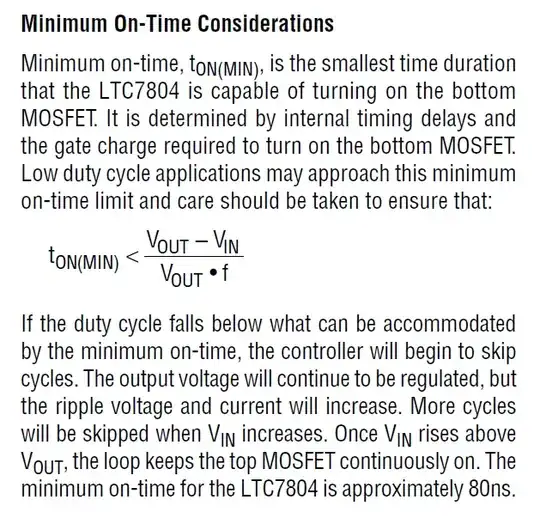

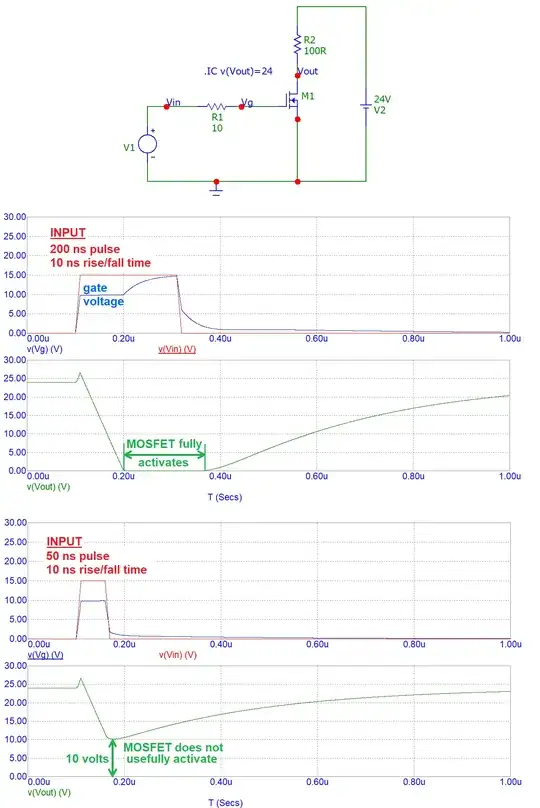

Does the minimum on-time depend on the MOSFET or not? It seems that it does not depend on the MOSFET, but I agree on the fact that if we took a bigger MOSFET, it will take much more time to switch ON, so it seems to have an effect on the minimum on time and on the output ripple. How can the manufacturer give minimum on-time without specifying the conditions on the MOSFET?

When we look at what is the maximum input voltage? The formula given in the datasheet does not depend on the size of the MOSFET, so it appears that the size of the MOSFET has no effect on the minimum on time. Here is an example to get Vin_max from this datasheet.