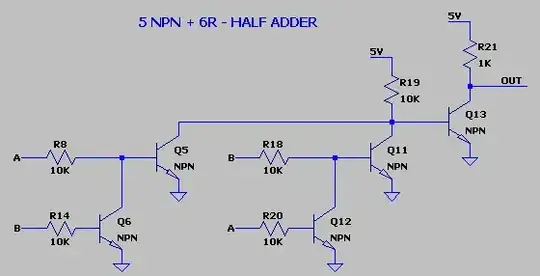

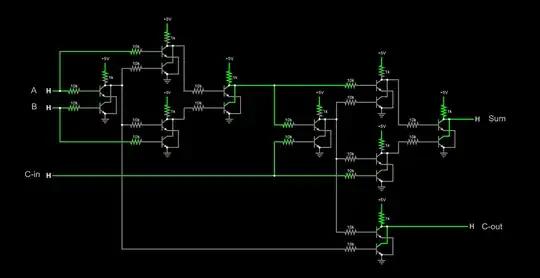

First of all, some of your resistor values need adjusting.

R16, R24, R25 need to be higher (like 10K).

Q6 needs a resistor on its base (like 10K).

Generally speaking, all collector and base resistors can be higher (like 10K) except the ones at the output (R20 and R23), which would be lower (like 1K).

If the output of any NAND stage drives only one base, then you can omit the base resistor.

R9, R10, R21, R22 are not needed.

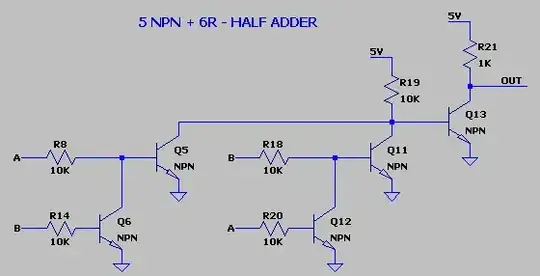

If you fix the resistor values, your half adder design for A/B with output at R8 is basically correct in that it implements the half adder truth table. Let A, B be int input and H be the half adder result at R8 then...

A B H

0 0 => 0

0 1 => 1

1 0 => 1

1 1 => 0

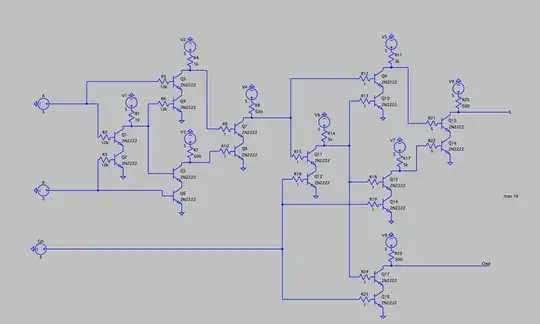

The carry logic is not correct. Your current design produces...

H Cin Cout

0 0 => 1 (should be 1 for A=B=1, but should be 0 for A=B=0)

0 1 => 0 (should be 1 for A=B=1, but should be 0 for A=B=0)

1 0 => 1 (not correct)

1 1 => 1 (correct)

The problem is that the carry logic in your design only depends on the half adder result and the input carry. For cases (A=1 and B=1) H is 0, so it gives incorrect results for those cases.

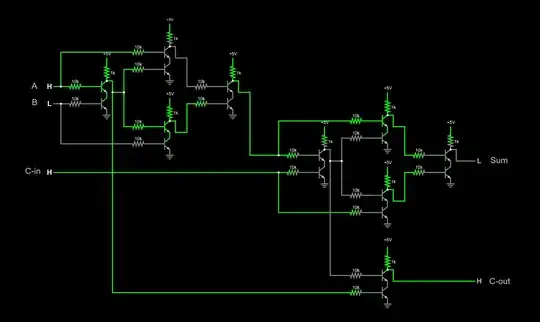

The truth table for a full adder should look like

A B Cin S Cout

0 0 0 => 0 0

0 0 1 => 1 0

0 1 0 => 1 0

0 1 1 => 0 1

1 0 0 => 1 0

1 0 1 => 0 1

1 1 0 => 0 1

1 1 1 => 1 1

Designing this out of NAND gates is of course not the most efficient design. Here are some examples that use less transistors/resistors.