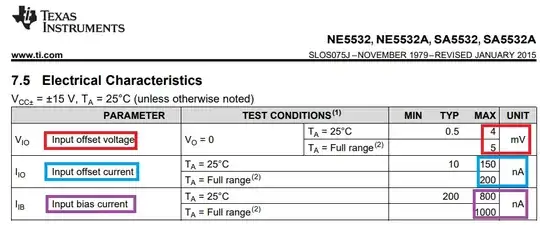

The NE5532 isn't good for these types of low-offset output voltage applications. There are several pointers in data data sheet: -

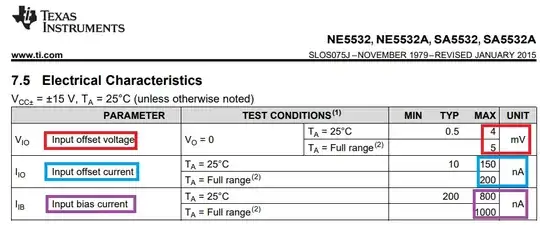

Input offset voltage

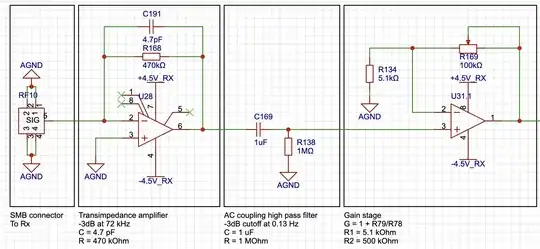

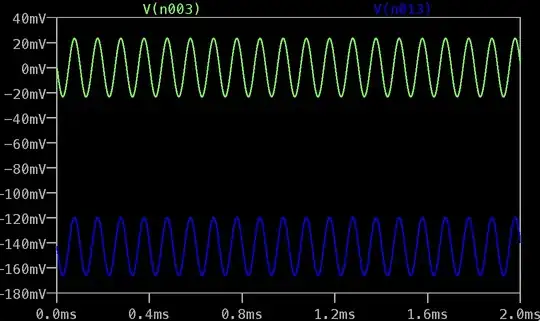

At your maximum gain (set by R169) of about 20, a typical input offset voltage of 0.5 mV will produce an output offset error of 10 mV. Far, far worse if the offset is not close to typical. I mean it could be as high as 4 mV at ambient temperature.

Input bias current

Input bias current will flow into R138 and typically, will produce an effective input offset voltage of 2 volts. This gets amplified and too bad, the op-amp output hits the end stops.

Input offset current

The data sheet gives you this figure to help you decide the final error due to bias currents. Input bias currents can be largely cancelled in many BJT op-amp circuits by using matching resistors in both inputs but, offset current tells you how far this can work. With a typical offset current of 10 nA and a resistor of 1 MΩ (R138), the effective error voltage at the input could still be 10 mV and, with your gain at a max level of 20, the output offset would be 200 mV.

What you should consider doing about offset/bias currents

Maybe try using a capacitor in series with R134; this makes the DC gain of the final stage unity. Of course, the capacitor has to be big enough so as not to reduce gains at low frequencies. If 20 Hz is your lower range you would need a capacitor of 2.2 μF in series with R134.

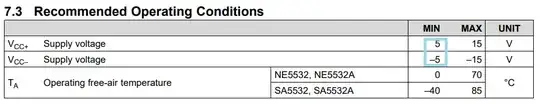

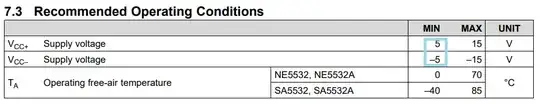

Recommended power supply minimal value

You are running it at +/- 4.5 volts but, the minimum recommended supply is +/- 5 volts: -

How to determine what's a suitable op-amp