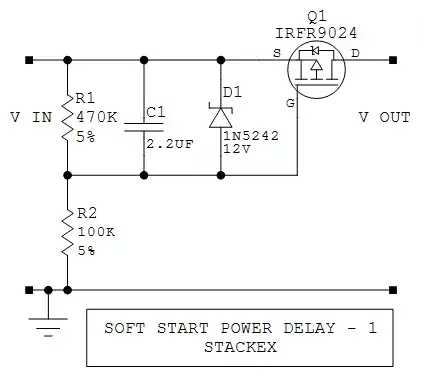

I have a 100W D class amplifier that runs on 24V. It uses 2 x TPA3116D2 IC for amplification. I also have a 24V 16A power supply. I need to provide a soft start circuit for this, because the amplifier is not protected from pops and clicks. I came up with the circuit below. It uses parts that I already have at hand. I ran a simulation and it seems to be right, but I have doubts.

I was not working with electronics in the last 6 months, and I'm not too familiar with analog circuits. I wanted to get an opinion before I built this circuit. I don't need a complete analysis, just a quick look. Does it have some obvious design flow? Is there anything that must be changed in order to work?

Thanks

ADD: One answer suggested modifying the amp instead of the power supply circuit. The amp is commercial product. I do not want to make any modifications to it."

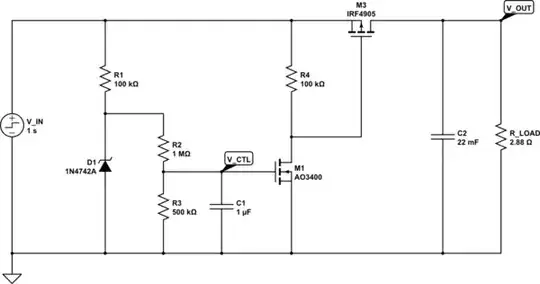

simulate this circuit – Schematic created using CircuitLab