I want to connect a 3.3V TFP401 to a 2.5V spartan 6 LX45T FPGA. It looks like each device is tolerant to the other device's voltage:

TFP401:

DVDD Min: 3.0V Nom: 3.3V Max: 3.6V

Input voltage range, logic/analog signals Min: –0.3V Max: 4V

High-level digital input voltage(1) Min: 2V Max: DVDD

Low-level digital input voltage(1) Min: 0V Max: 0.8V

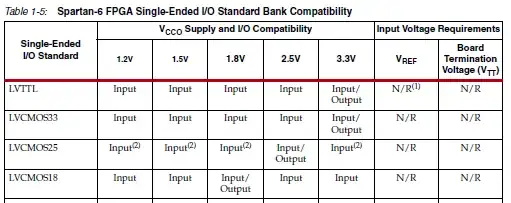

Xilinx Device:

This means that both are going to be transmitting at their respective voltages and are tolerant to receiving at the opposite voltage. I can't see anything wrong with this?

I'm just not sure about one thing: Do I have to be concerned about current drive strengths? If a device drive current is spec'ed to drive a voltage to 2.5V within a specified time, and the receiving device expects a 3.3V input with different high/low thresholds, then the input slew rate could possibly be out of spec since the signal takes longer to be detected as "high" on the receiving end?

I don't think this is a big issue because I can specify in my timing that the signal is a LVCMOS33 signal on a 2.5V line and the FPGA can compensate accordingly. Also I can change the drive strength on the FPGA as needed. I just want to be sure that this is really the case.

Clarification: At the moment my intention is to use LVCMOS33 for inputs and LVCMOS25 for outputs. I've never seen this done before. Good idea, bad idea?

Edit 1: Implications of using LVCMOS25 for in and out:

Case 1: FPGA out, TFP401 in.

FPGA out 2.5V.

FPGA Output Low is 0.4V max

FPGA Output High is 2.1V min

TFP401 in 3.3V.

TFP401 Input low is 0.8V max <-- Fine. FPGA out low is below TFP by 0.4V.

TFP401 input high is 2.0V min <-- Borderline. FPGA out high is above TFP by 0.1V.

Case 2: TFP401 out, FPGA in.

TFP401 out 3.3V.

TFP401 Output low is 0.8V max

TFP401 Output high is 2.4V min

FPGA in is 2.5V.

FPGA Input low is 0.7V max <-- Problem. TFP out low is above FPGA by 0.1V.

FPGA Input high is 1.7V max <-- Fine. TFP out high is above FPGA by 0.7V.

FPGA numbers taken from here, page 10.

TFP401 numbers taken from datasheet linked in first line.