(I am mainly from a software background and just started to work on an embedded platform. Excuse me if this is a naive question...)

I am planning to write a driver for an EEPROM which is connected to the MCU via an I2C bus. So I am reading a tutorial about the I2C bus.

The tutorial says:

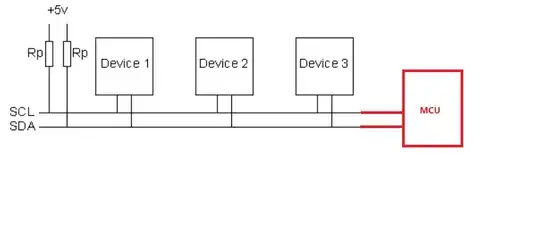

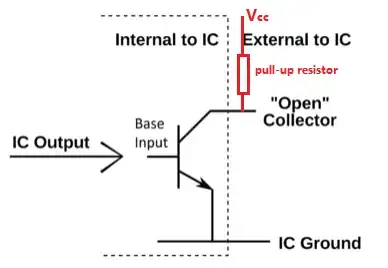

Both SCL and SDA lines are "open drain" drivers. What this means is that the chip can drive its output low, but it cannot drive it high. For the line to be able to go high you must provide pull-up resistors to the 5v supply. There should be a resistor from the SCL line to the 5v line and another from the SDA line to the 5v line. You only need one set of pull-up resistors for the whole I2C bus, not for each device, as illustrated below:

The red part in the above image is added by me. I guess that's how the whole picture is.

My questions are:

- Is my adding of the red MCU correct?

- The bold part the chip is the red MCU, right?

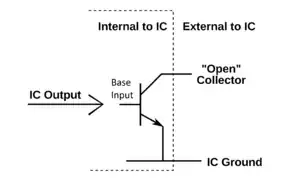

- Why is it true that the chip cannot drive it high? Is it unable or forbidden to?

- What does open drain mean in plain English?

I searched a bit but seems cannot find a clear explanation...maybe an analogy will help.