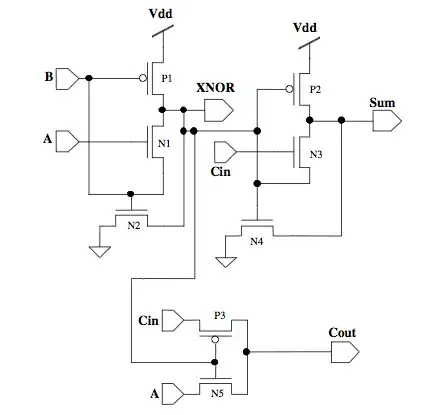

I am working on 8 Transistor full adder which is based on 3 Transistor XOR cell.

I have studied many IEEE Papers for 8 Transistor Full adder. All have same ckt as above.But the full adder is not working properly for all inputs values. I am using Tanner EDA at 180 nm tech and 5v supply voltage for simulation purpose.