There is a reason hardware is usually used to implement SPI slaves. It can be done in a microcontroller if you know the clock speed will be limited to some maximum value, a certain sequence is always followed by the master, etc. It is very difficult in the general case due to the possibly very short time between receiving information and then having to produce data based on that information.

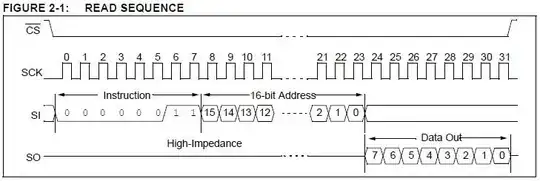

In your case you have less than 1 clock cycle to digest the last bit of the address before having to produce data that is presumably dependent on that address. If you know the system or have some control over it, you can have the master use a slow clock or at least stretch the clock between the 23rd and 24th rising edge. Otherwise, a non-hardware solution is probably not viable.

Let's say the clock speed is 10 MHz, which is perfectly valid for lots of SPI devices. That means you only have 100 ns between clock cycles. A dsPIC running at 40 MIPS can only do 4 instruction cycles during that time, which is very unlikly to be anywhere near enough to use the address, do the lookup, and start returning the data.

Not all things are possible just because you want them to be. This particular protocol was clearly intended for some kind of dedicated chip to implement on the slave side. Anything short of a FPGA isn't going to work for that in the general case.