Please refer to the following Verilog module:

module counter(

input wire clk,

input wire rstn

);

reg [4:0] counter;

// Powered by non-blocking assignments

reg enable1;

reg enable2;

reg enable3;

// Powered by blocking assignments

reg go_high_r1;

reg go_low_r1;

// Powered by non-blocking assignments

reg go_high_r2;

reg go_low_r2;

// Powered by continuous assignments

wire go_high_3;

wire go_low_3;

assign go_high_3 = (counter == 'd17);

assign go_low_3 = (counter == 'd28);

always @ (posedge clk or negedge rstn) begin

if (!rstn) begin

counter <= 'd0;

end else begin

// let it overflow

counter <= counter + 'd1;

end

end

// interaction b/w these signals below and enable1 signal is NOT clear

always @ (posedge clk or negedge rstn) begin

if (!rstn) begin

go_high_r1 = 'd0;

go_low_r1 = 'd0;

end else begin

go_high_r1 = (counter == 'd17);

go_low_r1 = (counter == 'd28);

end

end

always @ (posedge clk or negedge rstn) begin

if (!rstn) begin

go_high_r2 <= 'd0;

go_low_r2 <= 'd0;

end else begin

go_high_r2 <= (counter == 'd16);

go_low_r2 <= (counter == 'd27);

end

end

always @ (posedge clk or negedge rstn) begin

if (!rstn) begin

enable1 <= 'd0;

enable2 <= 'd0;

enable3 <= 'd0;

end else begin

enable1 <= (go_high_r1) ? 'd1 : (go_low_r1) ? 'd0 : enable1;

enable2 <= (go_high_r2) ? 'd1 : (go_low_r2) ? 'd0 : enable2;

enable3 <= (go_high_3) ? 'd1 : (go_low_3) ? 'd0 : enable3;

end

end

endmodule

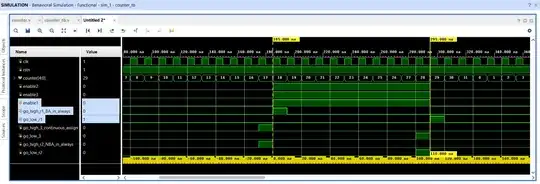

Waveform:

I am able to understand the interaction between enable_2 and enable_3 and corresponding control signals.

What I am not able to understand is that how enable1 gets its value without a single clock cycle delay (source: ans1, ans2) from the point of time when either go_high_r1 or go_low_r1 gets its value from the procedural block.

always @ *, I think that can save me from this confusion. Is there any other way of creating a control signal without using NBA? In this case, the signal might be dependent upon a lot of factors, so I cannot useassignstatement and I don't want to deal with the 1 cycle delay behavior of NBA (at least for control signals). If you'd like to share some of the discussions on the Verilog event queue, please do, as I suppose that these semantics remain same for SV too. – lousycoder Mar 09 '24 at 13:40