I’d welcome some advice on a hobbyist peripheral interface design.

This must use 74-series logic and have the lowest package count.

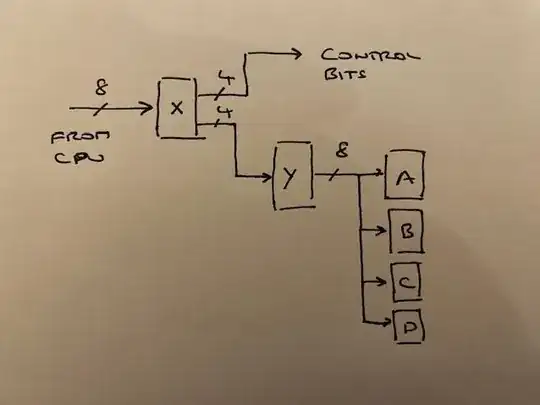

There is a notional CPU which is not shown in the sketch below. It is separate from the peripheral interface and connected to it via an external cable that has 8 data lines (plus ground), through which it can send a series of bytes/logic values. There's no specific software transfer protocol yet, this will be dictated by the needs of the interface design being discussed in this post.

The peripheral interface will have an 8-bit latch, [X] on the sketch below, like a 74HC373, that receives data from the CPU. There is a dedicated latch enable line under CPU control not shown in the sketch, but this cannot be repurposed - its sole role is to ensure that data is supplied to X correctly.

The 8-bit values latched into [X] are stable, until the next byte is sent. These bytes are sent by control software running on the CPU, which itself is clocked at around 1 Mhz.

I can’t add any more data lines to the cable, I only have 8 to work with.

From this single port, I need to populate four other HC373 type latches or registers [A, B, C & D] with specific data. Software can be written to get the CPU to send any required combination of 8-bit values, in order to achieve this.

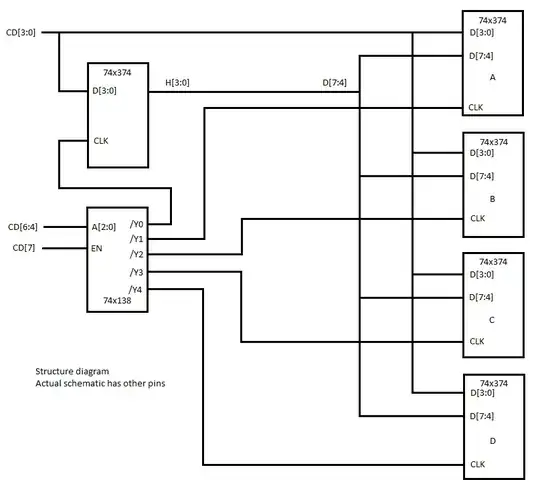

The current thinking is to use 4 bits of [X] for nibbles of data, and the other 4 as control bits. Two address bits to select [A], [B], [C] or [D] and a third control bit as a latch enable or clock line for them.

Next, that [X] connects to a dual 4-bit latch (perhaps a 74HC873) [Y], that recreates an 8-bit data byte from each pair of 4-bit nibbles using the fourth control bit (Hi/Lo). This then connects to one of [A], [B], C] & [D] depending on the control bits (00, 01, 10 or 11), and the data is latched/clocked.

In summary, the data values that end up in [A] thru [D] are envisaged as being sent by the CPU as 8 nibbles. Bits 0..3 at [X]'s output are those nibbles, and bits 0..4 provide the control bits that orchestrate this re-assembling of the data values.

I’ve got brain fog, and can’t come up with a circuit design despite numerous scribbles. It feels like there needs to be an additional control bit to latch data into the relevant 4-bit nibble latch, but there's probably a smart way to get around this.

Can anyone suggest a simple solution please?