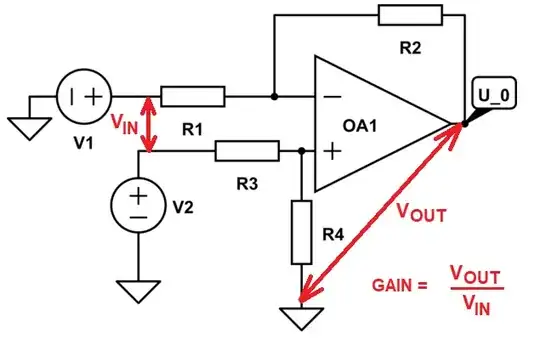

I'm having trouble understanding common mode voltage and its application when analysing a circuit. Let's say I have an op-amp in the following configuration from Sedra's Microeletronics book:

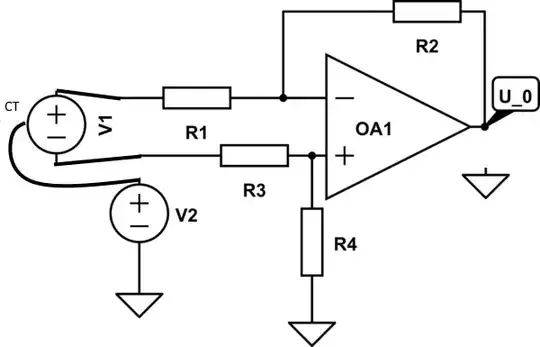

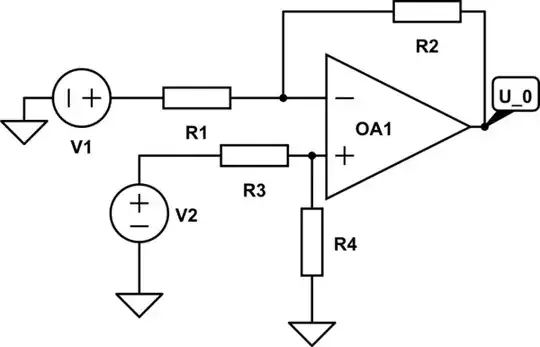

simulate this circuit – Schematic created using CircuitLab

Using node analysis I arrived at the expression:

$$ u_o = \cfrac{R_4}{R_1}\cfrac{R_1+R_2}{R_3+R_4}V_2-\cfrac{R_2}{R_1}V_1 $$

Let's say I want to determine the closed-loop gain \$G\$. As I understand it, the closed-loop gain is the op-amp gain at \$u_0\$, consisting of the common voltage gain summed with the difference gain. First question arises here: since my gain is the ratio of output by input voltage, what is the meaning of the gain here, since I'm giving two input voltages?

The book says that to ensure \$A_{cm} = 0\$ (which I understand as we do not want to amplify the undesirable bias coming from both op-amp inputs) then we set \$u_0 = 0\$ when \$V_2-V_1 = 0\$ and the common mode voltage \$v_{cm} \neq 0\$. Well, when we set \$u_0 = 0\$ aren't we imposing \$A_d = 0\$ and \$V_{cm} = 0\$? how does this help us find the gain?

The expression then becomes

$$ 0 = \cfrac{R_4}{R_1}\cfrac{R_1+R_2}{R_3+R_4}V_{cm}-\cfrac{R_2}{R_1}V_{cm} \Rightarrow R_4/R_3=R_2/R_1=K $$

So \$K\$ ensures that the common voltage gain is 0? Does it mean that for other resistor configurations, I'll have a common mode voltage gain but not for this one?

I understand lightly, but am still confused about it and I'm looking for help to clear it up with an explanation of what is happening.