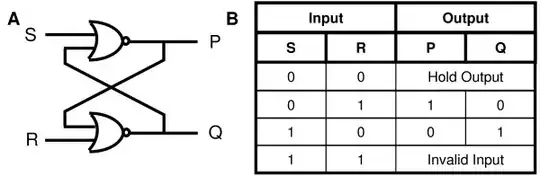

Actually your truth table has a slight problem.

Since a NOR gate output is LOW if either one is or both inputs are HIGH, so your SR latch will output P=Q=LOW if S=R=HIGH. It is a valid input for the circuit, causing valid output, if you don't consider the circuit as an SR latch.

Also you think the circuit as if it were somehow magically ideal, with either logic 0 or 1 digital inputs and outputs, and somehow quantized in time where it has a current state and next state like it was driven with a clock tick.

That only works in ideal world of mathematics and logic.

As you think of the circuit behaviour when power supply is turned on, please understand that the supply will also not be just off and then suddenly on at the next instant, that is physically impossible in real world.

In real world the logic gate is made of analog transistors and the signals are analog. The supply will be an analog signal too. Analog signals have finite bandwidth, meaning they rise and fall at some rate so the transitions happen in some time, as it would take infinite amount of bandwidth and energy to transition at infinitely fast rate in no time at all.

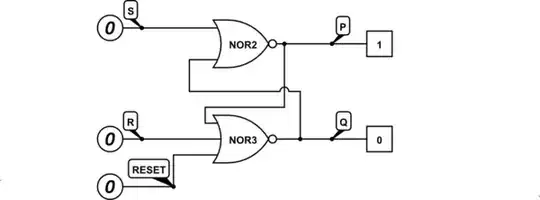

So holding the inputs S=R=LOW while turning the power supply on, the outputs don't have a valid state as the transistors don't have a valid supply voltage at first. Only when supply rises to high enough level, the transistors start to turn on and starting to pull the output PMOS transistors high.

So at some point the high output is high enough to turn on the output NMOS transistor, so for a moment there will be transistors pulling output both high and low until the supply voltage is high enough for the transistors to work strongly enough and end up into a stable state, which is basically random but due to transistor manufacturing tolerances and internal structures such as stray capacitances a certain logic gate may always end up in same state if you power it on identically multiple times.

So it does not hold any previous output as there is no previous state it is set to. That's why many circuits and ICs have a "reset" pin and a system may have a "powet on reset" circuit to make sure that all gates are "set" or "reset" on powering up to correct state as required by the system so the system does not start running on some random power-up state.

I assume unbuffered CMOS NOR gate in my example but there are also other logic families such as NMOS, PMOS, TTL, etc, so how a logic gate behaves depends on how it is built.