The question is confusingly asked, which might have been the whole point of it, as it mixes up some concepts from different aspects of what is know as "open loop synchronous timing". He might have been looking for you to clarify a few key concepts. Open loop in this context means that the delays/phase is uncontrolled.

Here is a brief overview to point into the direction at great simplification.

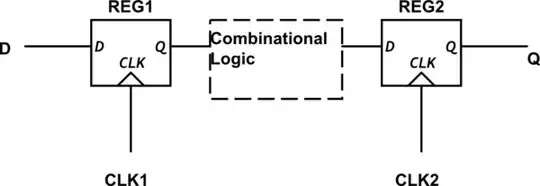

1) Global clock, edge triggered. What most people think of wrt to synchronous logic. The most popular for low end logic design because the edge triggered FF gives a simple model of sequential design, secondly, edged triggered FF are common deriving from TTL,CMOS and into the standard cell libraries that replaced them and thirdly most logic design courses only cover edge triggered designs.

- the draw back is that there are two constraints: The maximum delay of the logic must be less than a limit for the circuit to operate with a given cycle time. The minimum delay must be greater than a limit related to the clock skew for the circuit to operate at any clock frequency.

The minimum delay on the logic:

\$ t_{d,logic} \ge t_{skew}+t_{hold}-t_{prop,c->Q} \$

The minimum cycle constraint is:

\$ t_{cy} \ge t_{d,logic} +t_{skew}+t_{setup}+t_{prop,c->Q} \$

2) level sensitive, dual phase clocking. Is perhaps the highest volume design regime. because this is what is used in uprocessors and more complex devices. Of course there are many variants on this, here we just look at the non-over-lapped clock version. The logic is divided by the master and slave FF's and the minimum cycle time is limited only by the prop time of each logic block and the clock-> Q of the FF's. Clock slew (with in limits) does not figure into these designs and as a result they are more robust, faster and smaller. It's not clear to me why this isn't taught as often.

\$ t_{cy} \ge t_{d,logic1} +t_{d,logic1}+2t_{prop,c->Q} \$

This second case when there is no OL clocks, and there is no second logic block reverts to the first case.

3)Pipeline timing: which we'll not discuss here.