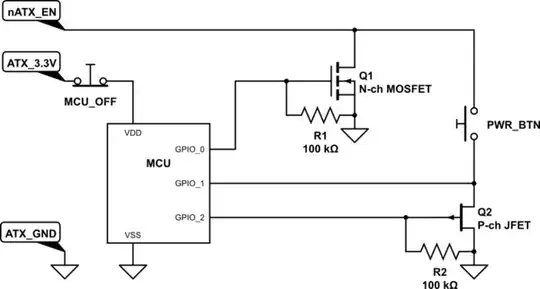

When the thing's powered up and and the PWR_BTN is being used as a user button, you take GPIO_2 high which you say "turns off Q2". I would expect, when you take GPIO_2 high, Q2 will not turn off until it has pulled GPIO_1 way down towards 0V. I would expect GPIO_1 to sit close to ground when GPIO_2 is taken high even without the PWR_BTN being pressed.

EDIT

For a p channel jfet the source is always the terminal which is at the more positive voltage of the two non-gate terminals.

The jfet is a depletion device which means that it is passing maximum current when the gate voltage is equal to the source voltage and, for a p-fet, the current conduction reduces more the further the gate is taken positive relative to the source. If the gate is taken far enough positive relative to the source then pinch-off is achieved where source to drain conduction ceases.

Usually care must be taken with jfets not to forward bias the gate diode. For a p-jfet care must be taken not to take the gate more than about 0.7 V negative relative to the source or the gate diode will be over driven and the jfet may be damaged.

The above describes the operation of a p-jfet. For a n channel jfet just reverse everything.

For an n-fet, the source is always the terminal which is at the more negative voltage of the two non-gate terminals. Again, being a depletion device the jfet achieves maximum drain to source conduction when the gate voltage is equal to the source terminal voltage. Conduction reduces more as the gate is taken negative relative to the source until the gate is taken sufficiently negative to achieve pinch-off at which point drain to source conduction ceases.

As with the p-fet, care must be taken to avoid damaging the fet which, for an n-fet, is likely to occur if the gate diode is forward biased which will happen if the gate is taken more than about 0.7 V positive relative to the source.

My interpretation of your circuit is that when you take GPIO_2 low you are forward biasing the gate diode but this shouldn't be a problem because the source terminal can follow the gate terminal but a small voltage above it, with a voltage drop across the microcontrollers internal pull-up resistor. If instead the p-fet's source had been hard wired to +3.3 V then I would have thought that taking the gate to 0V would have been a problem as too large a voltage would have been applied across the forward biased gate diode. With a typical microcontroller pull-up resistor value of say 20k ohms I would expect the current to be so low as to cause a quite a low voltage drop across the forward biased gate. If a much lower value of pull-up resistor was used then I would expect a larger voltage drop of say 0,7 V across the forward biased gate.

The problem I think I can see is that when GPIO_2 is taken high, if the source were to be pulled-up high by the internal pull-up resistor then the gate would be at the same voltage as the source, the p-fet would be fully turned on, current flows through the internal pull-up resistor which forces the source voltage to drop relative to the gate. The source will drop low enough to achieve a balance where less drop and the j-fet is turned on enough to make the source drop further but the source can't drop too far or the jfet will be turned off too much to allow enough current to flow for the required voltage drop across the internal pull-up resistor.

So, when PWR_BTN is being use as an ordinary user button I think that GPIO_1 will sit at some voltage significantly less than +3.3 V when PWR_BTN is not pressed.

I hope that gives you a better understanding and some ideas about possible potential problems.