In UCIe whitepaper, there is one paragraph describing the lanes in a cluster, as below:

The unit of construction of the interconnect is a cluster which comprises of N singleended, unidirectional, full-duplex Data Lanes (N = 16 for standard package and 64 for advanced package), one single-ended Lane for Valid, one lane for tracking, a differential forwarded clock per direction, and 2 lanes per direction for sideband (single-ended, one 800 MHz clock and one data).

I don't understand the emphsized phrases "single-ended, unidirectional, full-duplex" in the quote above: if a communication line is unidirectional, how it can be full-duplex? I guess I may be missing some background knowledge here.

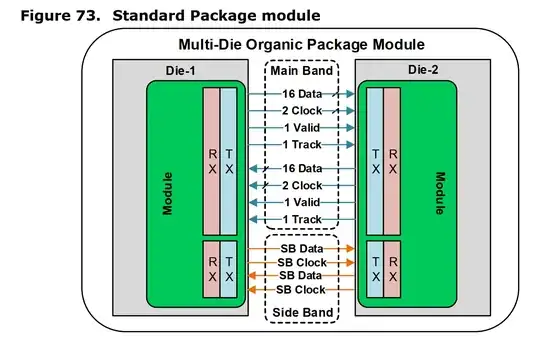

PS: the following picture from UCIe spec 1.0 suggests that: a lane is full-duplex and is composed by two single-ended uni-directional connections in different directions.