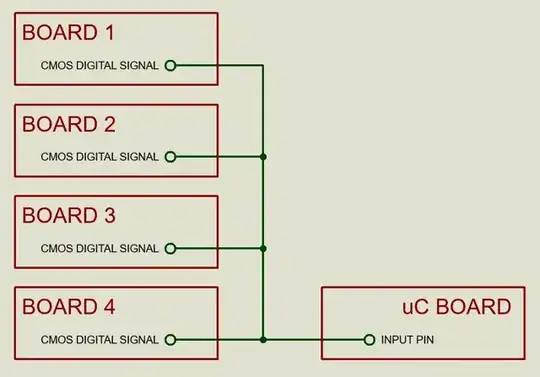

I have multiple IDENTICAL boards of which I plan to 'OR' the signal pins. I know that this can be done using a logic OR IC but that would require a modification on the microcontroller board which I cannot do. The modification must be made on the slave boards, and the slave boards must be identical. Any modification on any of the boards will also be present on the others. I plan the boards to be stacked on top of each other.

What happens with the configuration above is that none of the board can change states. The board is high by default, so when one board tries to go low the line will still be pulled up because of the other boards.

Is this possible?

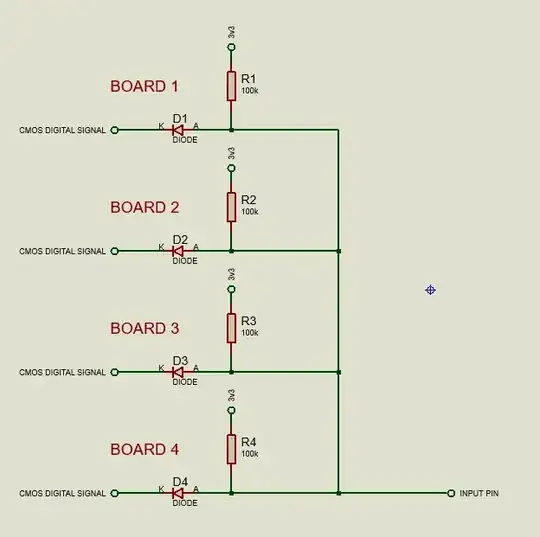

I was thinking along the lines of something like this, but I dont know if it can actually pull close to 0 because of the diodes: