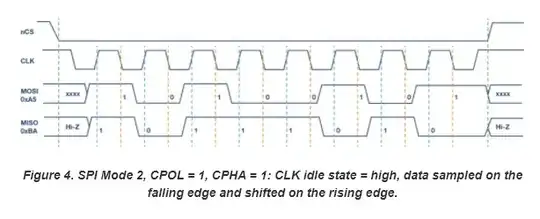

I am looking at the Analog Devices Introduction to SPI Interface and it has this diagram for SPI mode 2...

It shows that the first data bits do not appear on MOSI and MISO until after (1) CS goes low, and then (2) CLK goes low.

In other words, this seems to show that no data is sampled on the first falling edge of CLK after CS goes low.

Is this correct? I thought the first data bits were set up on the falling edge of CS and then sampled on the first falling edge of CS.

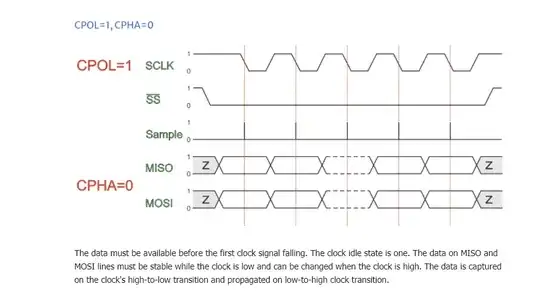

Here is another SPI mode 2 diagram from DLNWare that shows the data bits setting up on the falling edge of CS and then being sampled on the first falling edge of CLK thereafter...

It even specifically says "The data must be available before the first clock signal falling".

Which is right? In SPI mode 2 where CLK is idle HIGH and data is sampled on FALLING edge: after a falling CS edge, when is the first data bit read - on the first falling CLK edge or the second? Is it necessary to add an extra L/H/L CLK cycle at the beginning of each CS cycle that does not actually clock any data bits, so that there are n+1 CLK cycles to send n bits?