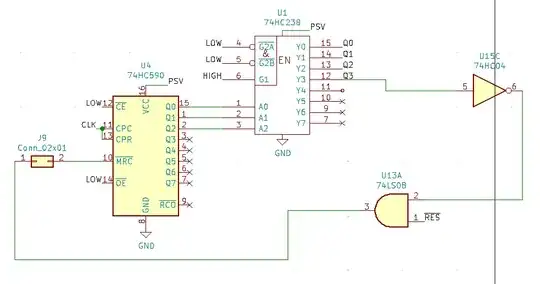

I'm (ab)using a 74HC590 binary counter as a 2-bit counter. The storage register clock is directly connected to the counter clock. I'm feeding the inverted 4th bit (bit 3) of the counter into ~MRC (master reset).

This works in principle, but state 0 lasts for two clock pulses. I am working on an existing PCB, so I am looking for a minimal fix, if there is one.

I could OR the common clock input with the non-inverted 4th bit to bump the storage clock by one, but that would not last, I suppose.

I guess I should ask a general question of perhaps more interest: what would be the recommended way of setting the modulo of the 590 counter to less than 8 bit?

recommended: try synchronous first. – greybeard Dec 28 '22 at 15:36