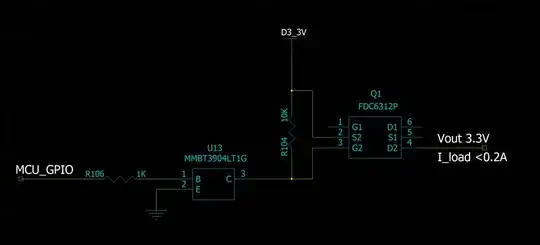

I have designed the following circuit using a PMOS (FDC6312P) as a load switch. The gate of the PMOS will be driven by an NPN transistor that can be controlled using the MCU's GPIO. I need to make sure that upon power-on, the load switch remains guaranteed off unless explicitly driven by the NPN through the MCU GPIO. Am I doing it right?

2 Answers

The transistors here are not that much important.

You need to know first the behavior of the GPIO pin of your MCU at power on.

Other than that, you may want to increase R106 at least 20x because more base current is of no use here.

You may as well add a resistor from U13 base to ground - just in case when GPIO sources some unwanted current when in high-impedance/indefinite/maybe pullup state. Some GPIOs do that.

- 9,184

- 11

- 35

-

Would replacing 1k with 20k in series to the base and a 100k resistor from base to the ground make sense? – Adnan May 18 '21 at 14:10

-

Probably. But see the MCU datasheet first. – fraxinus May 18 '21 at 14:16

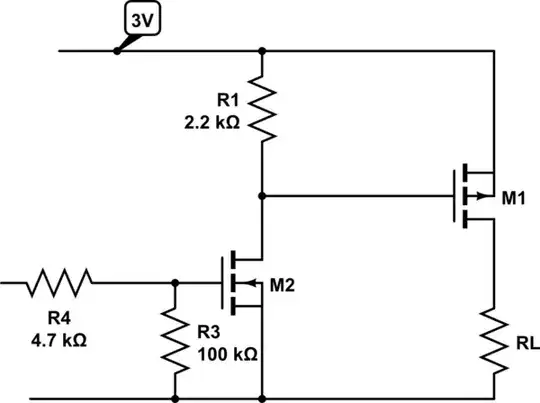

simulate this circuit – Schematic created using CircuitLab

R1 and R4 are subject to desired speed. I have changed the BJT with N-MOSFET because the voltage is very low (3V) and another 0.7V drop on BJT can be too much. The 100k resistor ensures that the gate is tied to GND even if GPIO is HiZ. The 2.2k resistor makes the P-MOSFET to stay in no-conduction mode. If you drive the GPIO Hi, then N-MOSFET conducts and turns on the P-MOSFET as well.

- 23,961

- 2

- 20

- 33