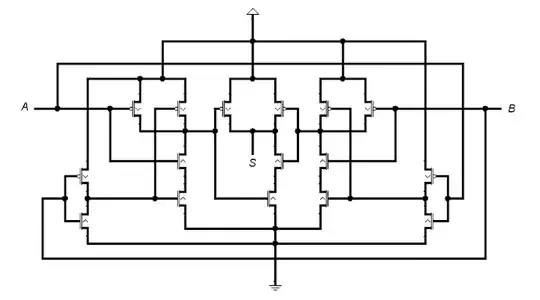

Since it has three NANDs and two NORs I guess it is an XOR, but doing the truth table I'm getting an OR expression. What's going on?

-

There are three NANDs and two inverters. No NORs. – Dave Tweed Apr 10 '21 at 03:24

-

2Isn't demonstrated effort required? Related: Closing homework questions with an attempt, Closing homework with no attempt as off-topic, and What does the community think about homework answers?. – Peter Mortensen Apr 10 '21 at 11:51

-

2From a comment: "...this is not a free design house, homework-writing service or an on-line technical encyclopedia, copied out to you on demand. People will help you take the next step if your questions shows that you've done as much as you possibly could on your own - which your post doesn't, I'm afraid. Please either revise your question showing your work and findings so far" – Peter Mortensen Apr 10 '21 at 11:54

3 Answers

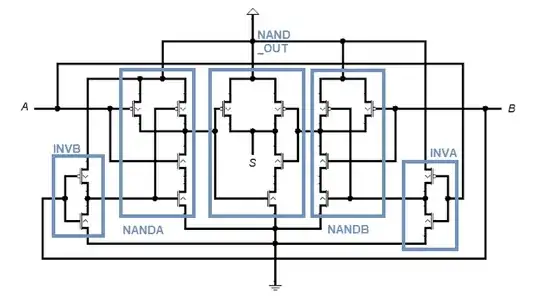

First, I "markup" your circuit drawing with logical element regions (two inverters, three NANDs):

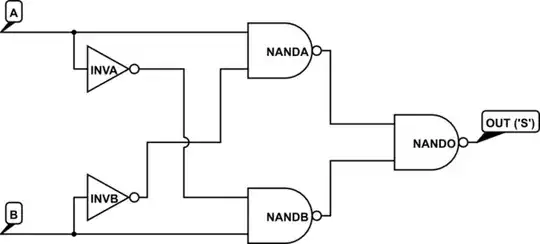

Then redraw it as digital circuits are drawn:

simulate this circuit – Schematic created using CircuitLab

and calculate the output:

NANDA outputs \$\overline{A · \overline{B}}\$

NANDB outputs \$\overline{\overline{A} · B}\$

NAND_OUT outputs \$\overline{\left(\overline{A · \overline{B}}\right) · \left(\overline{\overline{A} · B}\right)} = \overline{\left(\overline{A} + B\right) · \left(A + \overline{B}\right)} = \overline{\overline{A} · \overline{B} + A · B} = {A⊕B}\$

- 4,154

- 7

- 10

I would print out that picture four times, one for each input combination, and go through each one crossing out or shorting transistor source-drains as I go. That way you have a history of your work and the possibility to catch previous mistakes you made. When I did it I used Windows Snippet and doodled directly on-screen in snippet.

I can tell you that I get:

- S = 0 for AB = 00

- S = 0 for AB = 11

- S = 1 for AB = 10

Too lazy to do the last one but it took faster than I thought it would once you get into it so if I didn't make mistakes it can't be an OR and is probably an XOR. I would guess S = 1 for AB = 01 given the symmetry of the circuit which would make it an XOR but you shouldn't really make assumptions like that because your eyes might be missing something.

Make sure you are paying attention to the dots when wires crossover which let you know whether they are actually connected or not. I'm guessing this is probably what is happening plus you rushing through it. Go slow.

- 56,670

- 5

- 69

- 160

V.V.T's answer shows a neat approach to determine the behaviour of a logic circuit step by step even suitable for more complex circuits.

Anyway, for a simple circuit like the one at hand, featuring three NAND gates and two inverters, I would focus at those states that depend only on one input, particularly those of the NAND gates connected to the inputs:

- when the input \$A = 0\$, the output at the connected NAND gate must be \$1\$, independent from its other input;

- the same is true for the NAND gate at the other input when input \$B = 0\$;

- so the NAND gate at the output has got both inputs set to \$1\$ and therefore it returns \$S = 0\$; we have now determined what happens when \$A = B = 0\$, namely \$S = 0\$;

- now let us follow the path from input \$A\$ over the inverter to the NAND gate at input \$B\$: say \$A = 1\$, the inverter returns \$0\$, leading to the output state of \$1\$ at the NAND gate at input \$B\$, independent from the actual state of \$B\$;

- the same is true for the NAND gate at the other input when input \$B = 0\$;

- so the NAND gate at the output has again got both inputs set to \$1\$ and therefore it returns \$S = 0\$; we have now determined what happens when \$A = B = 1\$, namely \$S = 0\$;

- now let us take a look at the NAND gate at input \$A\$ and what input values are needed for its output to become \$0\$, which is the case when its inputs are both set to \$1\$, which is in turn achieved when we set \$A = 1\$ and, because of an inverter, \$B = 0\$;

- when the NAND gate at input \$A\$ returns \$0\$, the NAND gate at the output will return \$S = 1\$;

- finally, due to the symmetry of the circuit, the inputs \$A\$ and \$B\$ are interchangeable, so we have now already derived the full truth table;

So yes, it is an XOR gate:

A | B || S

---+---++---

0 | 0 || 0

0 | 1 || 1

1 | 0 || 1

1 | 1 || 0

- 415

- 3

- 15