I think some logic IC input can handle a range of lower voltage levels but will output at supply voltage...

What is the best way to achieve an input that can handle higher levels but output at a lower level for the next stage? Some logic ICs or circuits that can do this?

not dealing with high speeds, 5kHz max.

5v logic with 5-10V input range

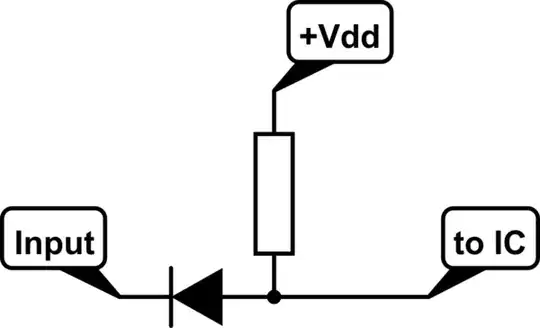

What about a zener on the input?

typical load would probably be driving 1 or 2 CMOS inputs, input impedance is not critial

– Jay Apr 13 '20 at 23:23And yes that sums it up.

– Jay Apr 14 '20 at 06:23