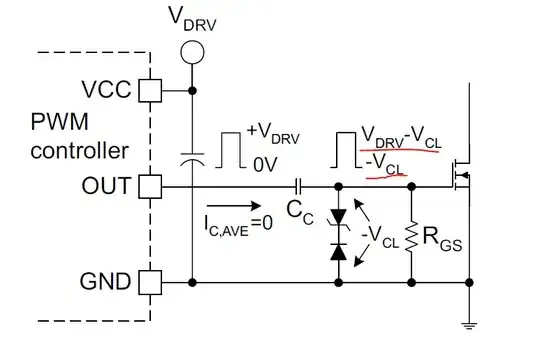

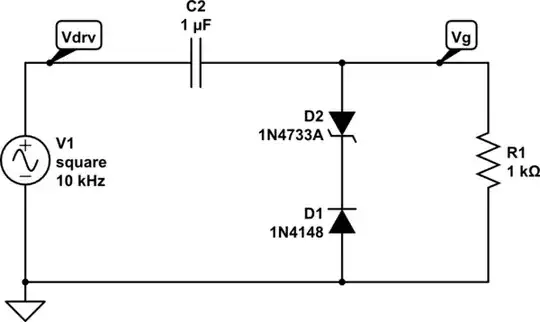

Here is the Following circuit :

I don't know how the application note can assert that the voltage after the capacitor is equal to Vdrv-Vcl or -Vcl according to the driver output as there is a resistor Rgs ? Even with the clamp circuit it is just an RC circuit. Where is my error ?

The picture is extracted from this application note written by TI. http://www.ti.com/lit/ml/slua618a/slua618a.pdf

Thank you very much,