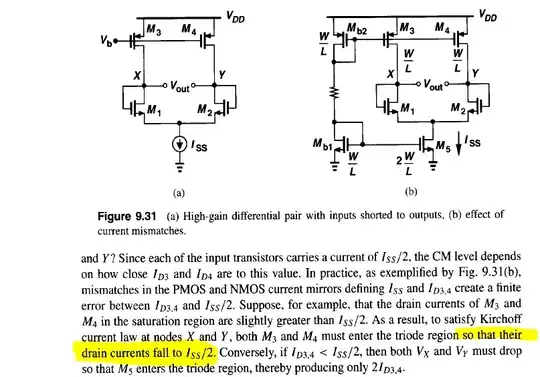

Consider the following circuit in Fig 9.31 (a)

Now, essentially, summarising the block of text, it seems that due to some mismatch between PMOS and NMOS devices or fluctuations in bias voltages, the current that Iss/2 pulls may not equal what the PMOS current sources and thus this leads to the voltage at X or Y increasing or decreasing until those currents match.

So problem solved right? Here come's my question, why do people and books say that without common-mode feedback, my output will get driven to the Vcc or GND rail if the currents matched? Won't the scenario I just explained happen and our MOSFETs may go into linear region but why would the outputs go to the rails? I don't see where that is coming from. I can understand if there's a huge mismatch that would happen but some mismatch, the voltage should just go up or down at the output, it shouldn't reach the rails.