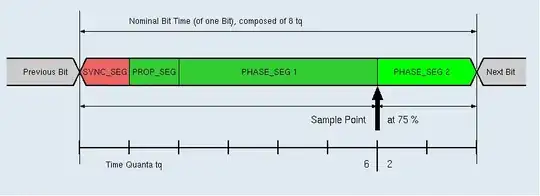

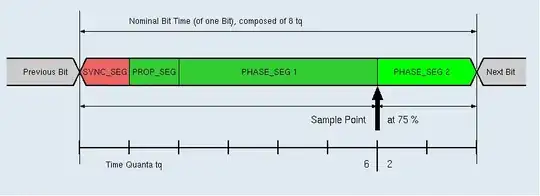

Depending on the peripheral reference clock, its possible prescaler, and the certain/target CAN speed you need, you need to configure the PHASE_SEG1 and PHASE_SEG2 duration--expressed in integer multiples of Time Quanta (tq)--so that in a nominal case (without adding/subtracting up to SJW tq's) the position of Sampling Point to be as close as possible to 87.5% of the nominal bit time.

In the picture below, it is assumed that the nominal bit time consists of eight (8) tq's. But in your particular design it could consists of any (of course, appropriate) number of tq's depending on the conditions listed above.

Therefore, for example, with a nominal bit time of 10 tq's at a prescaler of N/2, you could have another option with a nominal bit time of 20 tq's (twice bigger) at a prescaler of N (twice lesser), but of the same physical duration on the wire.

SJW is an additional, "independent" parameter related to a "real" situation on the bus and defines the number of tq's up to which the PHASE_SEG's could be variated ("tuned") depending on the real situation during the transmission/reception of each bit in the message.

Generally speaking, the PHASE_SEG1 duration could be prolongated by up to maximum SJW duration while the PHASE_SEG2 duration could be shortened by SJW down until to zero (but non less than zero).

The goal of such a "tuning" is to place the Sample Point into the "good" moment and to (re-)synchronize the "collective" behavior of nodes on the bus.

The cause of such a "tuning" lays in the recessive/dominant method of transmission on a CAN bus, during that, the real transition on the bus can take place far beyond the SYNC_SEG phase duration where it is assumed to be in the nominal case.

Is there any drawback to a longer SJW vs a shorter SJW?

A longer SJW could result in a more robust interaction, a shorter SJW could result in a faster transmission. Knowing nothing about a particular bus implementation, speaking on a drawback is a clear speculation having no ground under it.

Why wouldn't an SJW of two not be used by default?

At one time-defining profile and with one bus specifics it may be of one, at another time-defining profile and/or with other bus specifics it may be non-of-one. Neither default value is less speculative...