A variable in microcontroller RAM changes 50 times/second. Does that degrade the memory location of the MCU in long run? If so, how long is the memory location expected to be active?

3 Answers

SRAM, DRAM has infinite endurance.

FLASH, FRAM, and EEPROM have limited endurance.

SRAM is made with transistors or mosfets. It's an active component that loses its state when power is removed.

DRAM uses tiny capacitors to temporarily store data, these are continuously refreshed by the memory controller because these capacitors leak. Both DRAM and SRAM will work until material degradation renders the part unusable. (decades)

FLASH and EEPROM work similar, by using capacitive effects on fet gates, and these do have limited endurance. "Flash wear" is caused by erasing due to slowly accumulating charge around the flash cells during erase. When flash is erased, it is erased to a logic 1 by a "high" voltage.

FRAM works magnetically, it also has limited endurance. But the write cycles are in the trillions, almost infinite.

- 22,972

- 37

- 74

-

1You said, "FLASH, FRAM, and EEPROM have limited endurance" which is technically true but misleading because it is only part of the truth. Apparently, if you just flip the bits (XOR with 0xFF, then again) every once in a while, then FRAM has unlimited endurance. Please fix this in your answer. FRAM is an excellent technology. (Full disclosure: - I have nothing to profit from promotion of FRAM). – MicroservicesOnDDD Jul 10 '23 at 14:22

There's no such thing as RAM life expectancy. You may get this wrong impression because there is a limited number of erase cycles you may apply to EPROM and EEPROM (flash) cells.

For EPROM/EEPROM cells the reason you cannot erase them unlimited is they grow leaks with every erase cycle. It's like a bucket you handle not too carefully. But it's crucial for the function that the leaks are not too big, so the information is retained in the non-powered state.

For RAM, this problem does not apply:

DRAM is so leaky by design it looses information within a few ms, so the RAM controller has to read it out and refill as needed. Naturally, this only works when the RAM is powered.

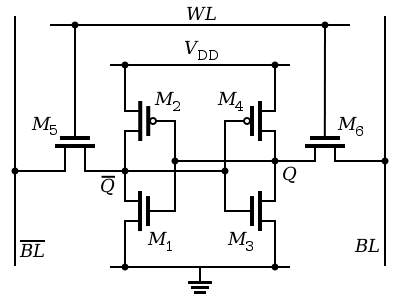

SRAM is also leaky but instead of a RAM controller, each single cell has a positive feedback circuit which keeps one of two buckets filled and the other emptied. Naturally, this only works when the RAM is powered.

- 14,276

- 1

- 21

- 35

I have found a document on soft error rates, which also mentions a hard error rate for SRAM. SRAM is typically used in microcontrollers, so it should be applicable.

The paragraph reads:

Quite aside from soft errors, particles with high energies can cause permanent damage to memory cells. These “hard” errors exhibit error rates that are strongly related to soft error rates [29], variously estimated at 2% of total errors [26] or “one or two orders of magnitude less than soft error rates – often in the range of 5 to 20 FIT [7]”. A one-bit hard error is correctable with ECC* , just as if it were a soft error; however, the error will recur each time the bad cell is used. As hard errors accumulate, they eventually render the memory device unusable. Recently, a very few state-of-the-art memory devices have incorporated new self-healing technologies to repair hard errors; these technologies are outside the scope of this paper.

So 5 to 20 FIT. If FIT doesn't mean anything to you: The Failures In Time (FIT) rate of a device is the number of failures that can be expected in one billion (10^9) device-hours of operation.

So the mean time between failures (MTBF) would be 10^9 hours divided by 20, and that is rougly 5700 years.

And typically these FIT numbers are rather pessimistic.

You will probably not see a SRAM fail which doesn't see abnormal stress. You might notice, that in the described failure model, there is no relation to the use of the cell. Like the others said, a properly designed SRAM will not degrade through usage.

- 17,674

- 1

- 34

- 60

-

3It should be noted that you will get damage on any semiconductor if you bombard them with high energy particles. Which is why rad-hard parts are often shielded. – Jeroen3 Apr 25 '18 at 17:50

-

1Whilst true, this is a different issue from the OP's question. Damage from high-energy particles is an entirely external effect, in the same way as damage from static discharge or physical impact. The OP asked about possible damage to RAM due to the memory cell changing state in normal operation. – Graham Apr 25 '18 at 21:45

-

@Graham the fact that for hard errors the normal usage is not even considered speaks for itself in my opinion, which I expressed in the answer as well. – Arsenal Apr 26 '18 at 07:01

TI MSP430FR series has an FRAM read and write endurance of minimum 10^15 cycles.

– Peter Karlsen Apr 25 '18 at 13:15