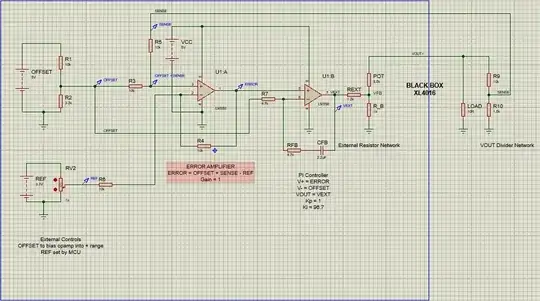

I have the following circuit set up to control VOUT (labelled SENSE on my Excel test results).

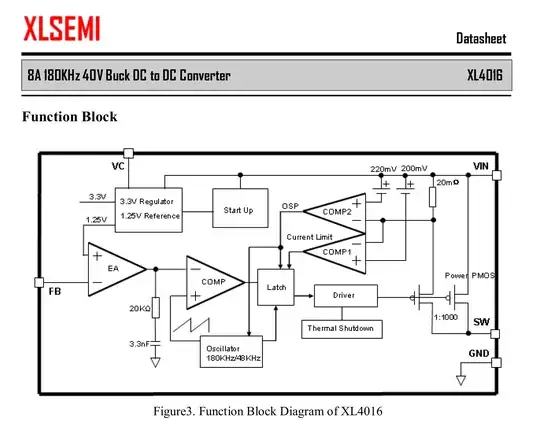

Note that the node between REXT, POT, and R_B is called VFB. It goes to the FB pin of the XL4016 chip, which I didn't have on Proteus so I left it as a black box.

I am expecting to see: 1. When OFFSET < ERROR, positive integration, therefore PI controller goes high, VEXT increases. 2. When OFFSET > ERROR, negative integration, therefore PI controller goes low, VEXT decreases. 3. Regardless of the value of VEXT, VFB should stay at 1.25V*.

*This is explained by the datasheet for the XL4016 buck IC. The VFB pin is connected to a comparator with a reference value of 1.25V, which is how the buck converter works normally to maintain a constant output voltage.

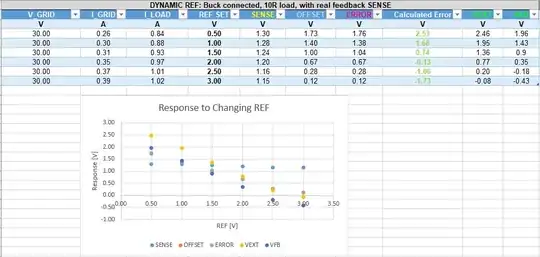

However, I am not seeing these results. Instead, when I ramp up the REF signal to the error amplifier, I get the following:

Also, for some reason, the OFFSET and ERROR signals are matching each other. The ERROR comes from the error amplifier on the left, and follows the formula: ERROR = OFFSET + VOUT(LOW) - REF. This is fed into the + pin on the PI op amp and compared to the OFFSET signal which is sent to the - pin of the PI op amp. Since the two inputs are identical, I would expect the output of the PI controller (VEXT) to fluctuate about neutral, NOT ramp down.

So I have several questions. 1) Why is VFB not being maintained at 1.25V? 2) Why is the OFFSET responding to changing REF, and why does it match the ERROR signal? 3) Why is the VEXT (output of the PI), not reflecting the relationship of its inputs?

Overall, I am able to achieve VOUT control by varying the REF, so the overall objective is achieved, but I have no idea why my PI controller and the XL4016 are suddenly not working.

Note: they work just fine when the buck converter has no load attached, and no VOUT feedback to the system (I use a fake VOUT/SENSE input in those cases).

As for the schematic, please do advise what is improper about it; I'd be happy to improve. I haven't been an EE for 40+ years like yourself.

– YNGVV Apr 03 '18 at 07:39As for the hysteresis R3/R5, could you please clarify what you are concerned with? I chose 10k input resistors for those two signals, OFFSET and SENSE, to keep the gain of EA = 1.

– YNGVV Apr 03 '18 at 07:58