Indeed, it is usually a problem. Now, lets' have a look at the datasheets of some PHY chips, just to check.

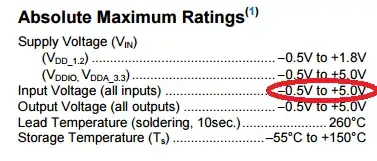

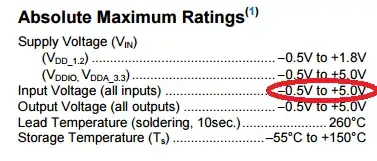

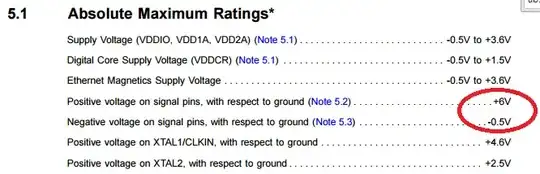

Here is the Absolute Maximum Ratings of a typical ETH PHY, the KSZ8051 (from Micrel, now Microchip):

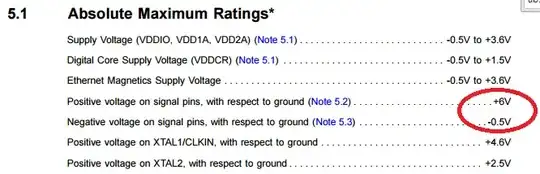

Here is the Absolute Maximum Ratings of another one, the LAN8720 (I know, it's Microchip too, but they just bought everybody, it's not my fault):

So, as long as you are within this, it is fine. And with normal levels on the ethernet pairs and proper biasing of the transformer, you should be within this.

When the chip can be damaged by providing an input voltage while powered off, the datasheet indicates something like VCC+0.5V as its maximum input voltage. Here, we have an absolute value, so the input voltage tolerance does not depend whether the chip is powered or not.

Note that in the case of ethernet PHYs, all solutions of course take this into account, and no PHY can be damaged when there is signal but no power applied. This is the same for RS-232, RS-485 drivers, CAN drivers, etc... They are all immune to this problem, or nobody would buy them.

EDIT

Apologies... Following a few comment exchanges with @SimonRichter (see below), I realized that actually, what I say above would be correct and complete for any kind of physical interface except ethernet. The reason being: there is a transformer to isolate the node and the cable. The center tap of the transformer is usually tied to the supply rail to bring the signal within the input range specs, and all is fine. But when the circuit is not powered, the supply rail is zero and the signal becomes centered around ground. So it would exceed the maximum ratings when going negative.

So I started thinking hard 1, but did not find an explanation.

What I guarantee for sure is that it is not a problem. Ethernet PHYs and ethernet signaling are designed so that it doesn't break when an unpowered node is connected to a powered node, and you don't have to take particular precautions in your circuit to be safe in this respect.

But it's true that I had a look at several PHY datasheets, and the maximum ratings are not actually enough to guarantee that, and I never saw a chapter that explains why it is still safe.

So, well, I must admit I don't know the full answer, actually.

Therefore, I have set a bounty on that question so somebody explains us, with concrete facts, how it can be safe, or provide actual proofs that the datasheets are lacking some information (like an extended safe range for TX/RX pairs that is not specified).

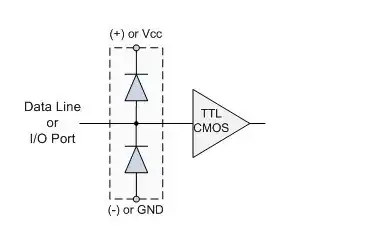

1 - First, I thought maybe the protection diodes would bring back the signal within range. But it can't: the center tap would then have to supply the whole circuit, which doesn't make sense. Then I thought maybe the link detection protocol was specified in a way that it can actually never happen: the normal ethernet signal never being sent unless the other side identifies that the distant node is actually active and powered. But it doesn't make sense either: the link detection protocol is using normal ethernet signaling.