Im having trouble getting my head around using two mosfets to pass AC.

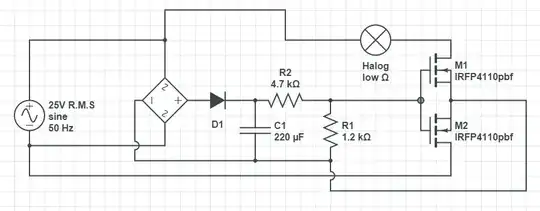

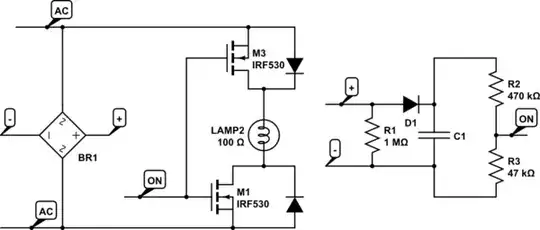

I have reduced my schematic to its bare bones to help keep it un-cluttered. The aim of this circuit is to use PWM to dim a bulb running AC. the PWM circuitry and gate drive is omitted.

I am taking 25V AC rms through a bridge rectifier to allow me to maintain a DC level at the gate through the voltage divider with the aid of a cap.

The above circuit caused my lower fet to fry and also the insulation on the wire from the source to my bridge negative terminal melted.

Any assistance is greatly appreciated!

EDIT:

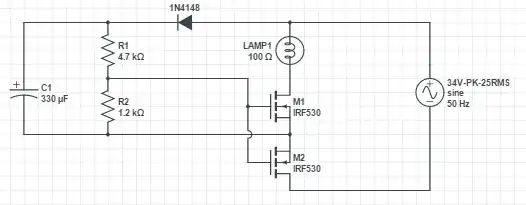

I have amended the circuit to eliminate the short.

But i am unclear as to how the VGS limit of 20V is not exceeded. The output of the Divider is around 7V (more than enough for my fet). So if the top rail initially peaks at 34V and charges the cap, then the cap will hold the gates at 7V relative to the source ( and cathode of the cap). For the opposing cycle, the lower rail peaks at 34V, or relative to the top rail/capacitor -34V (i believe this is where my logic is incorrect). When the bottom fet opens up, this -34v potential is passed to the source before travelling through the body diode of the top fet to the load. if this is true, the VGS potential would be 7V (positive at the gate) + the negative 34V peak at the source passed from the drain = 41V.

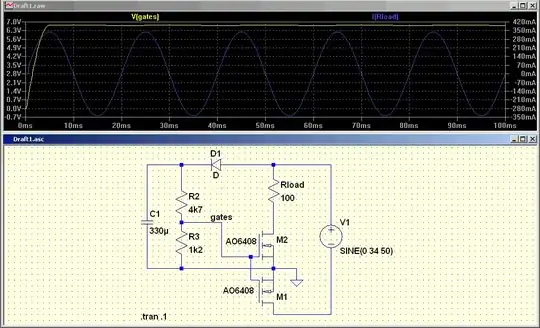

I have been told in a forum elsewhere this reasoning is incorrect and a simulation proves the VGS potential to maintain at 7V.

I do not doubt the simulation may be correct, however i am failing to prove to myself either way what is happening.

switching the gate at 20Khz, so i am using a high frequency diode for D1, the bridge is rated for low frequencies.

my apologies for applying the term ground incorrectly. old hobbits die hard.

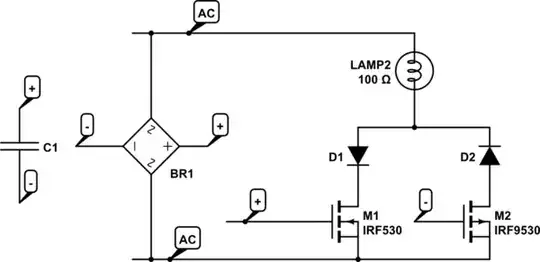

Could you recommend a better solution to this circuit? Or will a resistor from common source to the -VE bridge terminal suffice?

Thanks for this, it has been frustrating me all day!

– engineeroverhere Jan 23 '15 at 17:50THanks!

– engineeroverhere Jan 26 '15 at 10:22