The LC-3 is a classic fixed-size-instruction CPU with 16-bits registers, 16-bits addresses, and 16-bits instructions. Hence there can't be a (single) instruction that can load any 16-bit value into an address.

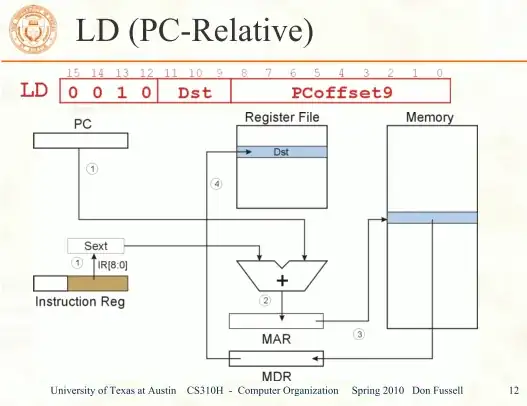

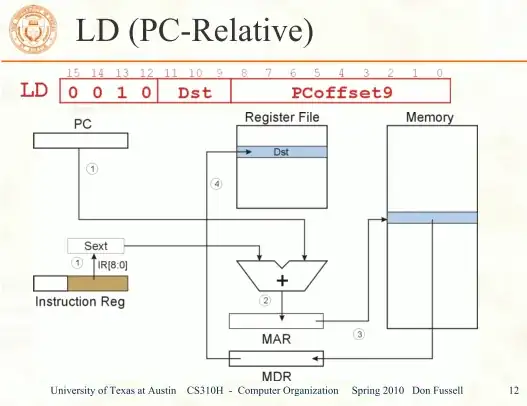

The classic way to solve this (the ARM for instance uses this too) is to use PC-relative addressing to access a memory word where the 16-bit value is stored. This memory word must be sufficiently 'near' to the instruction to be addressable by the (in this case 9 bit) offset that fits into the instruction.

See Lecture_10-310h.pdf (second hit gooling "LC-3"), sheet 12:

One (inefficient) way to have the memory word nearby is to store it in a word that is jumped over:

LD reg, <offset of dataword>

BR continue

dataword: < put 16-bits data here >

continue:

Note that this leaves some details for you to find out, in particular how the offset is to be calculated and represented.

(The more efficient way is to group a bunch of such data words just outside a subroutine, so the jump instructions are not needed.)

Another classic (somewhat faster and compacter) way to solve this problem (loading N bits of data in a fixed-size-N-bits instruction set) is to load the data in two instructions. Somehow one instruction must load different bits than the second. In the classic ARM this could be done by first loading a shifted literal into the upper 16 bits, and the OR or ADD with a literal into the lower 16 bits. But the LC-3 does not seem to have an effective shift instruction (would require a sequence of adds), so this would be very ineffective.