# Sequential Signal Assignment (4A)

| Copyright (c) 2025 - 2012 Young W. Lim.                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

| Please send corrections (or suggestions) to youngwlim@hotmail.com.                                                                                                                                                                                                                                                                                                              |

| This document was produced by using OpenOffice and Octave.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

#### Sequential Signal Assignment Statement

```

process(clk) is

begin

if rising_edge(clk) then

a <= b;

b <= c;

c <= a;

a <= c;

end if;

end process;</pre>

```

Within a process, statements are indeed carried out sequentially.

However, <u>values</u> assigned to signals are <u>not</u> carried out <u>immediately</u> but <u>scheduled</u> to occur at the <u>end</u> of the process.

when the assignment  $\mathbf{c} \leq \mathbf{a}$ ; is carried out, the <u>value</u> of  $\mathbf{a}$  is still the value a had at the <u>start</u> of the <u>process</u>.

This is because the assignment  $\mathbf{a} \leq \mathbf{b}$ ; has <u>not</u> yet been carried out and  $\mathbf{a}$  has not changed.

#### Multiple Assignment

```

process(clk) is

begin

if rising_edge(clk) then

a <= b;

b <= c;

c <= a;

a <= c;

end if;

end process;</pre>

```

```

In fact, the assignment a <= b; will never be carried out because of the fourth assignment a <= c;, which will be scheduled to occur at the process end instead.

```

This behaviour reflects the behaviour of real logic circuitry, which is what VHDL was designed to do.

#### Think reverse order

try to read statements in reverse order:

```

a <= c -- the a register gets whatever was in the c register</li>

c <= a -- the c register gets whatever was in the a register</li>

b <= c -- the b register gets whatever was in the c register</li>

a <= b -- this statement is <u>ignored</u>.

```

no two drivers for a single FF input

multiple <u>assignments</u> to a <u>signal</u> in a <u>process</u> statement, only the <u>last assigned value</u> is considered

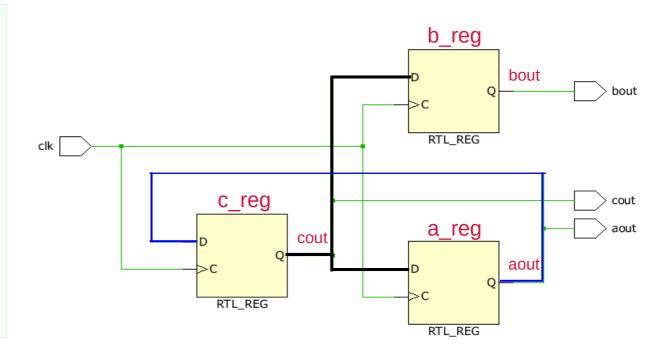

### Synthesis Results (1)

```

process(clk) is

begin

if rising_edge(clk) then

a <= b;

b <= c)

c <= a;

a <= c)

end if;

end process;</pre>

```

b\_reg and a\_reg are exactly the same(i.e. they each clock the same signal in and out).

If this simple example were to be synthesized, one of them would almost certainly be removed, and bout would be tied to aout.

In fact, it took some keep attributes just to tell Vivado not to eliminate the **b** reg for the RTL.

### Synthesis Results (2)

```

process(clk) is

begin

if rising_edge(clk) then

a <= b;

b <= c)

c <= a;

a <= c)

end if;

end process;</pre>

```

synthesized results by Vivado

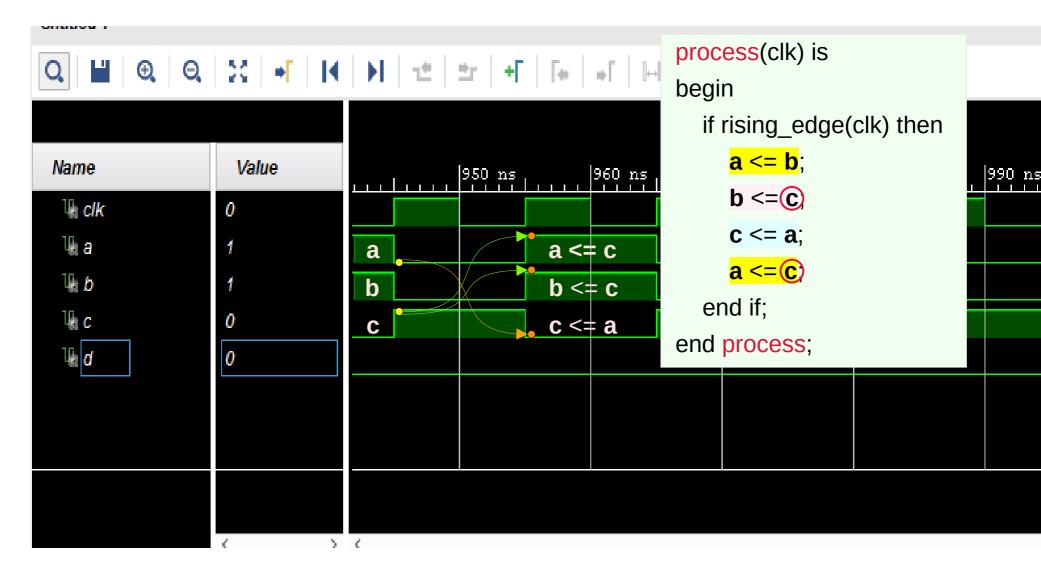

#### Simulation Results (1)

In VHDL, statements in process are executed sequentially.

a, b, c and d are signals

$a \le b$ ;

c <= a;

At the end of the process

old value of **b** assigned to **a**. and

old value of **a** assigned to **c**.

statements in process executed sequentially, but the signals don't get the new values before end of the process.

the initial value of the signal before rising edge of clock.

**a**=1; **b**=1; **c**=0;

In the rising edge of clock, the statements in the process executed. so at the end of process

the new value of signals are:

a = old c = 0;b = old c = 0;

c = old a = 1;

```

process(clk) is

begin

if rising_edge(clk) then

a <= b;

b <= c)

c <= a;

a <= c)

end if;

end process;</pre>

```

#### Simulation Results (2)

## Sequential Statement

#### Updating signal values and running processes

signals represent the interface between the <u>concurrent</u> domain of a <u>VHDL</u> model and the <u>sequential</u> domain within a <u>process</u>.

A VHDL model is composed of several processes that <u>communicate</u> via <u>signals</u>.

At simulation, all hierarchy of the model is removed and only the processes and signals remain.

The simulator <u>alternates</u>

between <u>updating signal</u> values and then

running processes activated by changes

of the signals listed in their sensitivity lists

### Signal Assignment

Signal assignment may be performed using a sequential statement or a concurrent statement.

The sequential statement may only appear <u>inside</u> a process, while the <u>concurrent</u> statement may only appear <u>outside</u> processes.

The sequential signal assignment has a single form, the simple one, which is an unconditional assignment.

The concurrent signal assignment has, in addition to its simple form, two other forms: the conditional assignment and the selective assignment.

## Sequential Signal Assignment Statement

The sequential signal assignment has the same syntax as the simple form of the concurrent signal assignment;

the difference between them results from context.

the sequential signal assignment has the following syntax:

signal <= expression [after delay];</pre>

as a result of executing this statement in a process, the expression on the right-hand side of the assignment symbol is <u>evaluated</u> and an <u>event</u> is <u>scheduled</u> to change the value of the <u>signal</u>.

### When the process suspends

The simulator will only change the value of a signal when the process <u>suspends</u>, and, if the after clause is used, after the delay <u>specified</u> from the current time.

Therefore, in a process the signals will be updated only <u>after</u> executing <u>all</u> the statements of the process or when a wait statement is encountered.

Typically, synthesis tools do <u>not</u> allow to use <u>after clauses</u>, or they <u>ignore</u> these clauses.

### Delay and synthesis

The after clauses are <u>ignored</u> not only because their interpretation for synthesis is <u>not</u> specified by standards, but also because it would be difficult to guarantee the results of such delays.

For example, it is not clear whether the delay should be interpreted as a minimum or maximum propagation delay.

Also, it is not clear how the synthesis tool should proceed if a delay specified in the source code cannot be assured

#### Multiple assignments

A consequence of the way in which signal assignments within processes are executed is that when more than one value is assigned to the same signal, only the last assignment will be effective.

Thus, the two processes are equivalent.

```

proc7: process (a)

begin

z <= '0';

z <= a;

end process proc7;

proc8: process (a)

begin

z <= a;

end process proc8;</pre>

```

### When the process suspends

In conclusion, the following important aspects should be taken into consideration when signal assignment statements are used inside processes:

- Any signal assignment becomes effective only when the process suspends.

Until that moment, all signals keep their old values.

- Only the <u>last assignment</u> to a signal will be effectively executed.

Therefore, it would make no sense to assign more than one value to a signal in the <u>same process</u>

#### Zero time

No event will ever occur while a process is running!

When a process is woken by an event, it runs to <u>completion</u> ("end process") or an explicit "wait" statement, and goes to sleep.

This takes, notionally, ZERO time.

if you have loops in your process, they are effectively unrolled <u>completely</u>, and when you <u>synthesise</u>, you will <u>generate</u> enough hardware to run <u>EVERY</u> iteration in parallel.

Also, any procedures, functions etc, take zero time - unless they contained an explicit "wait" statement

(in which case the process suspends at the "wait", as if the procedure had been inlined).

#### No event when a process is running

No event will ever occur while a process is running!

When a process is woken by an event, it runs to <u>completion</u> ("end process") or an explicit "wait" statement, and goes to sleep.

This takes, notionally, ZERO time.

Throughout this process, all signals have the value they originally had when the process woke up, and any signal assignments are stored up, to happen later.

Variables update immediately; later statements in the process see the new value).

#### Restarting a process

When the process suspends (at "wait" or "end process"), nothing happens until ALL the other processes also suspend.

(But remember they all take zero time!).

If a process suspends at "end process" it will <u>restart</u> from the beginning when its <u>sensitivity list wakes</u> it up.

If it suspends at an explicit "wait", that "wait" will specify an event or future time, which will restart it after the "Wait".

#### NOTES:

- 1 : do not mix the sensitivity list and Wait styles in the same process!

- 2: Wait Until some <u>event</u> is synthesisable (though some tools may object); Wait for some <u>time</u> is simulation only

#### Performing all the signal assignments

THEN all the signal assignments are performed.

Since <u>all processes</u> are <u>asleep</u>, this eliminates all race conditions and timing hazards.

Some of these assignments (like '1' to a clock) will cause events to be scheduled on processes sensitive to them.

## Delta cycle

```

After <u>all</u> the <u>signal assignments</u> are done,

the <u>time steps</u> forward one infinitely short tick (called a <u>delta</u> cycle),

and then all the <u>processes</u> with <u>scheduled events</u> are <u>woken</u>.

```

This continues until a delta cycle occurs in which <u>NO new events</u> are scheduled, and finally the simulation can advance by a real time step.

```

process(clk)

begin

if rising_edge(clk) then

A <= B;

B <= A;

end if;

end process;

```

is hazard-free in VHDL.

## Verilog

If you ever need to use Verilog, be aware that some of this happens differently there, and you <u>cannot</u> rely on the same level of <u>predictability</u> in simulation results.

In synthesis, of course, we generate hardware which will take some real time to execute this process.

However, the synthesis and back-end tools (place and route) guarantee to either obey this model faithfully, or fail and report why they failed.

For example, they will <u>add up</u> all the real delays and verify that the sum is less than your specified clock period. (Unless you have set the clock speed too high!).

#### Zero time

So the upshot is, as long as the tools report success (and you are setting the timing constraints like clock speed correctly) you can pretend the above "zero time" model is true, and the real hardware behaviour will match the simulation.

Guaranteed, barring tool bugs!

#### Reentrant?

When starting out using VHDL (or any other HDL for that matter), it is hugely important to discard all notions of sequential code, and instead focus on the flow of data through the hardware.

In <u>hardware</u>, everything is inherently <u>parallel</u> (everything happens simultaneously), but uses <u>constantly changing data</u> (input signals) to calculate <u>constantly changing results</u> (output signals)!

Without going into more advanced topics such as variables, wait commands etc., everything within a process happens simultaneously.

If conflicting things occur within the same process (multiple writes to the same signal), the <u>last statement</u> in the process <u>wins</u>, which is often where confusion about "sequential" code in VHDL comes from.

#### Delta

This works due to the way that values are assigned to signals.

When assigning a value to a signal, the value of the signal does <u>not immediately change!</u>

Instead, the assigned value is <u>remembered</u> and will be <u>committed</u> as the actual signal value <u>later</u> (in preparation for the <u>next delta cycle</u>, which is effectively the next quantum of time).

Since the <u>next</u> <u>delta cycle</u> will <u>not</u> <u>begin</u> <u>until</u> all <u>processes</u> from the <u>previous</u> <u>delta cycle</u> have <u>completed</u>, <u>signal</u> values will only <u>change</u> when <u>no</u> <u>process</u> is <u>running</u>.

Once all signals have <u>changed</u>, the <u>next delta cycle begins</u> and any <u>process sensitive</u> to one of the <u>changed</u> <u>signals</u> will be executed.

### Combinatorial loop

If a process is sensitive to a signal it also <u>writes</u>, you have what is known as a <u>combinatorial loop</u>, e.g., a gate where the output feeds an input.

This is (almost) always an <u>error</u> in your circuit, and will usually cause simulators to enter an <u>infinite</u> <u>delta-cycle loop</u>.

#### References

- [1] http://en.wikipedia.org/

- [2] J. V. Spiegel, VHDL Tutorial, http://www.seas.upenn.edu/~ese171/vhdl/vhdl\_primer.html

- [3] J. R. Armstrong, F. G. Gray, Structured Logic Design with VHDL

- [4] Z. Navabi, VHDL Analysis and Modeling of Digital Systems

- [5] D. Smith, HDL Chip Design

- [6] http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html

- [7] VHDL Tutorial VHDL onlinewww.vhdl-online.de/tutorial/