# Nesting, Tail Chaining, and Late Arrival

Copyright (c) 2023 - 2014 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using LibreOffice.

#### Based on

ARM System-on-Chip Architecture, 2<sup>nd</sup> ed, Steve Furber

Introduction to ARM Cortex-M Microcontrollers – Embedded Systems, Jonathan W. Valvano

Digital Design and Computer Architecture, D. M. Harris and S. L. Harris

ARM assembler in Raspberry Pi Roger Ferrer Ibáñez

https://thinkingeek.com/arm-assembler-raspberry-pi/

#### Nesting, Tail Chaining, and Late Arrival

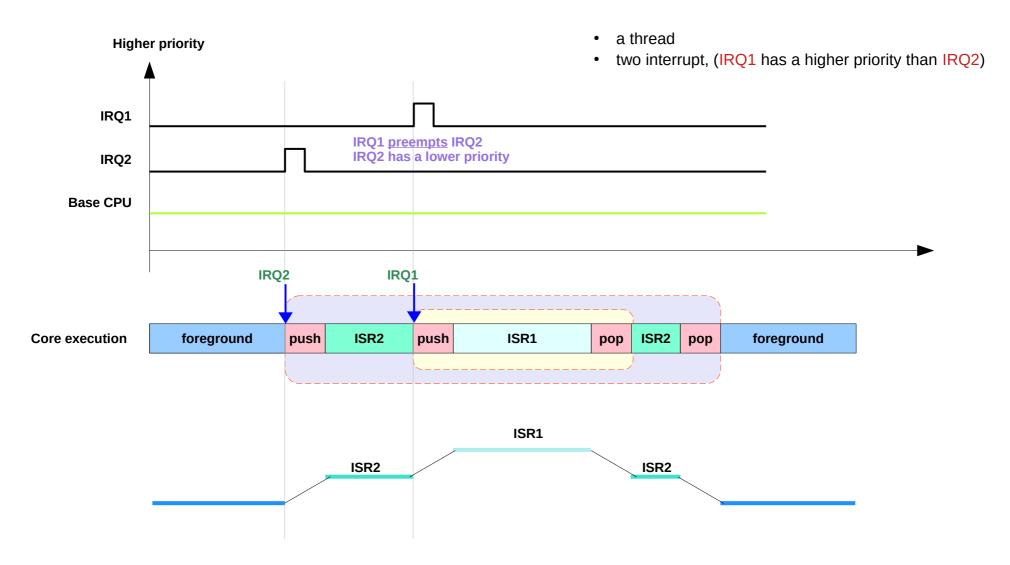

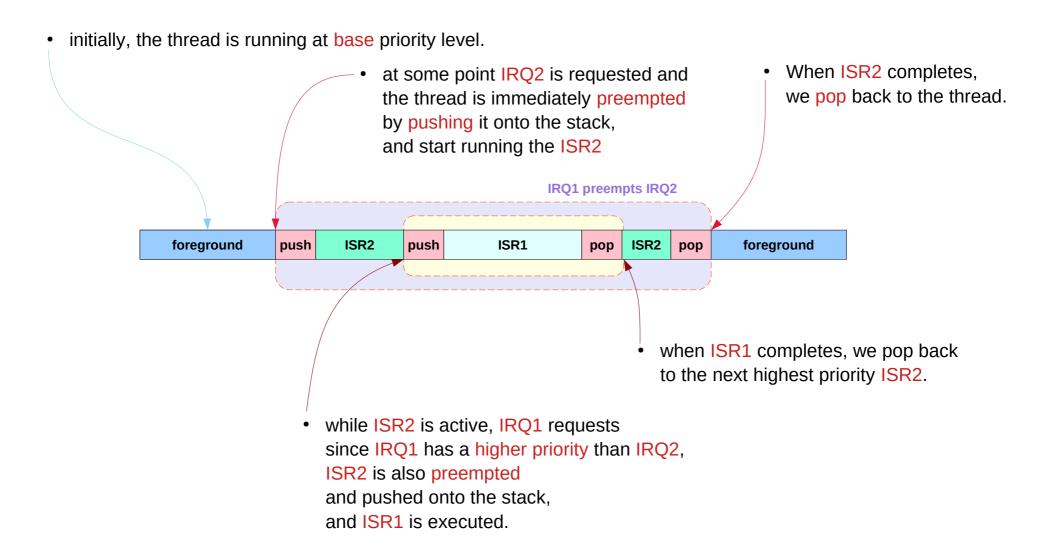

#### preemption

interrupts the <u>context</u>

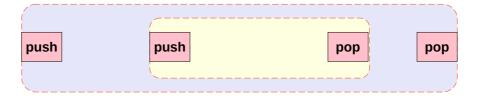

by <u>pushing</u> registers onto a stack

and <u>popping</u> them later

to return to the interrupted <u>context</u>

#### tail-chaining

allows <u>additional</u> <u>handlers</u> to be executed <u>without</u> additional <u>pushing</u> and <u>popping</u> of registers.

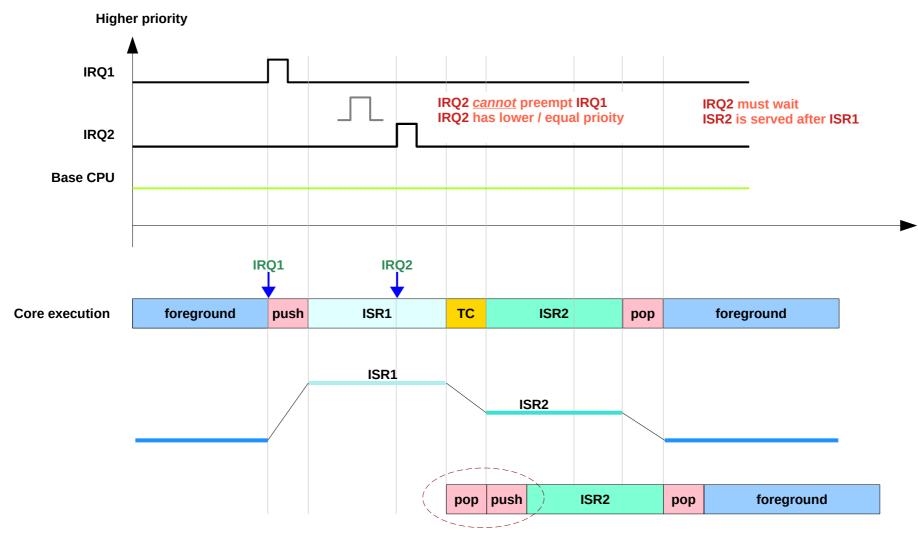

consider a diagram

<u>priority</u> on the <u>vertical</u> axis

time on the horizontal.

https://www.coursera.org/lecture/armv8-m-architecture-fundamentals/nesting-tail-chaining-and-late-arriving-examples-FmA6E-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-and-late-arriving-examples-fundamentals/nesting-tail-chaining-arriving-examples-fundamentals/nesting-tail-chaining-arriving-examples-fundamentals/nesting-tail-chaining-arriving-examples-fundamentals/nesting-tail-chaining-arriving-examples-fundamentals/nesting-tail-chaining-arriving-examples-fundamentals/nesting-tail-chaining-arriving-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-examples-fundamentals/nesting-exam

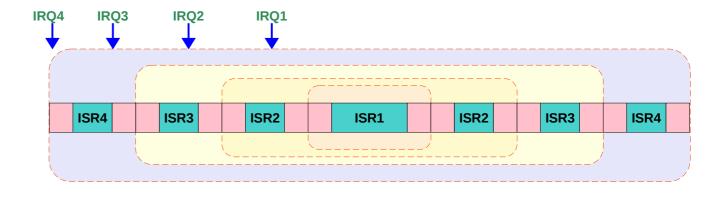

## Nesting (1)

## Nesting (2)

## Nesting (3)

- The benefit

- distinct levels of priority

- always working on the most important task

- *minimize* the interrupt latency for the highest priority interrupt at any time.

- The cost

- a few cycles performing housekeeping (push, pop) around the interrupts.

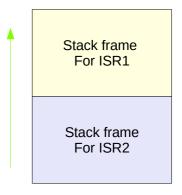

- creating multiple stack frames increases the need for stack memory consumes energy for several memory cycles

increasing stack

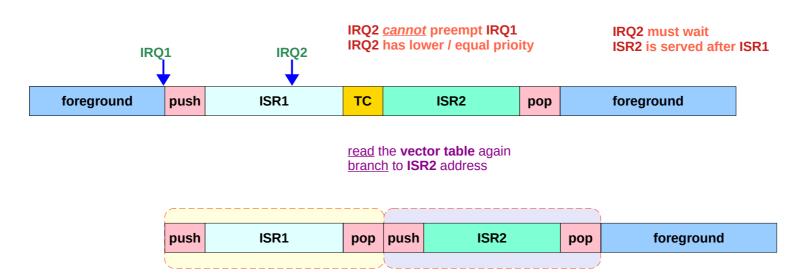

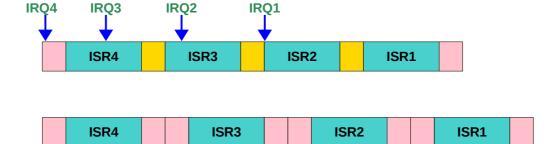

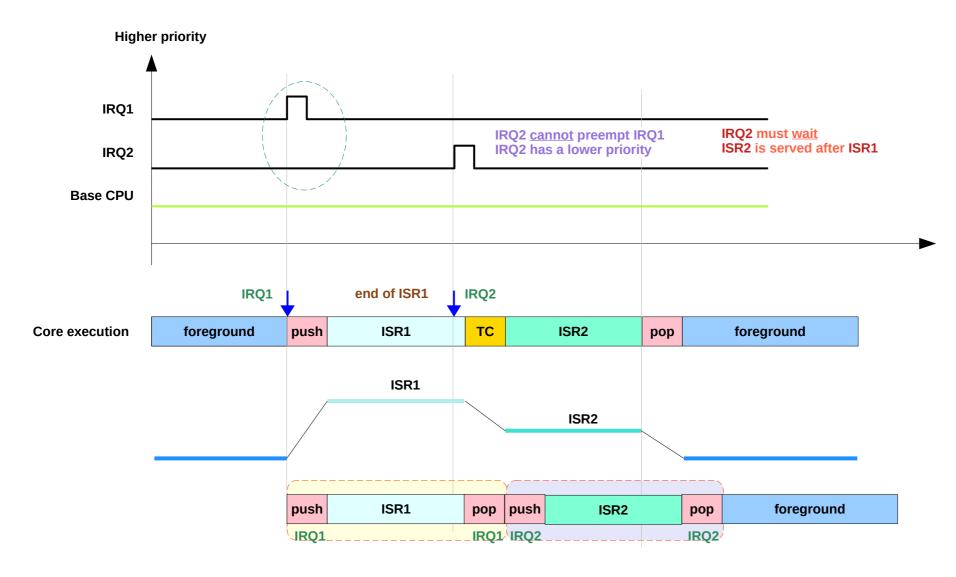

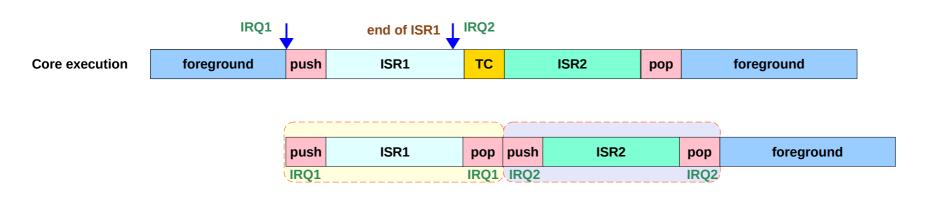

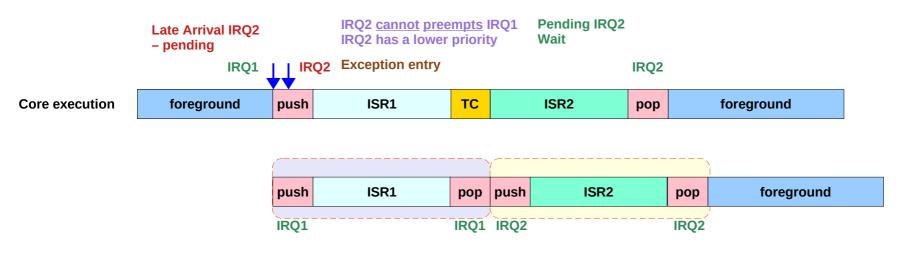

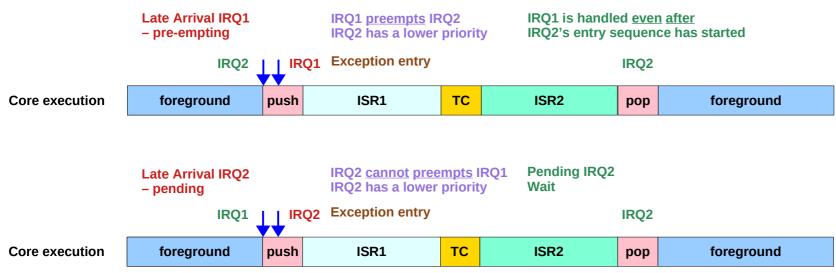

#### Tail chaining (1)

#### Tail chaining (2)

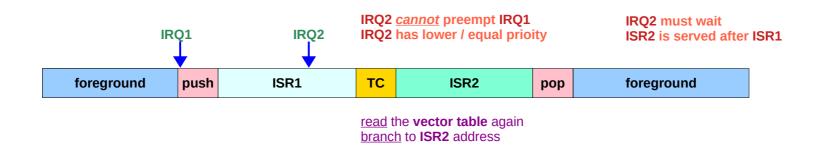

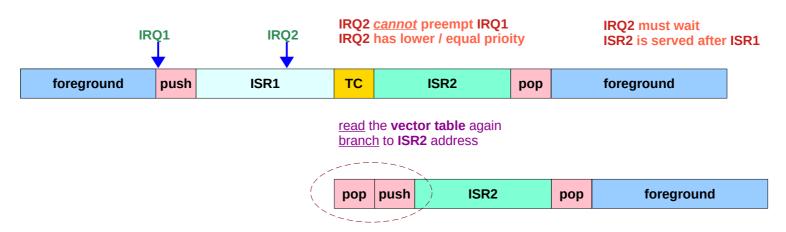

- Priority (IRQ2) ≤ Priority (IRQ1) thus IRQ2 <u>cannot preempt</u> IRQ1.

- IRQ1 preempts the thread with a stack push.

- while ISR1 runs, IRQ2 occurs,

- IRQ2 remains pending

- ISR1 runs to completion

- At the end of ISR1, the NVIC then arbitrates to IRQ2 and runs ISR2 simply by reading the vector table again and branching to that address.

- Only when ISR2 is completed and there are no other pending interrupts, the stack popped to return to the thread.

## Tail chaining (3)

Priority (IRQ2) ≤ Priority (IRQ1) thus IRQ2 cannot preempt IRQ1. At the end of ISR1, (tail chaining)

the NVIC then arbitrates to IRQ2 and runs ISR2

simply by reading the vector table again and

branching to that address.

- In this case, there was <u>less</u> *control* of interrupt <u>latency</u>.

- <u>cannot</u> preempt, must wait

- as any <u>lower</u> or <u>equal</u> <u>priority interrupt</u>

that <u>occurred</u> while another interrupt was <u>active</u>,

would have to <u>wait</u> for that active ISR to <u>complete</u>.

#### Tail chaining (4)

#### to perform the housekeeping between interrupts

- fewer cycles were spent

- less energy used

- less memory space used

#### these lead to

- better overall throughput

- lower power

- smaller memory requirements

#### Tail chaining (5)

ARM recommends programming interrupts into as few priority levels as needed, and therefore, using tail-chaining as widely as possible to take advantage of these benefits.

**Priority (IRQ4)**

- < Priority (IRQ3)

- < Priority (IRQ2)

- < Priority (IRQ1)

- 4 distinct priority levels

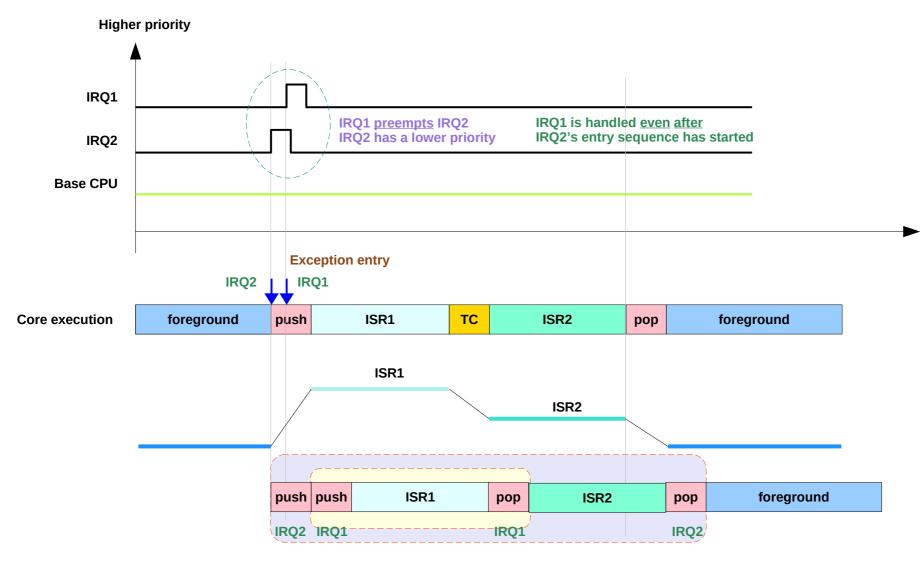

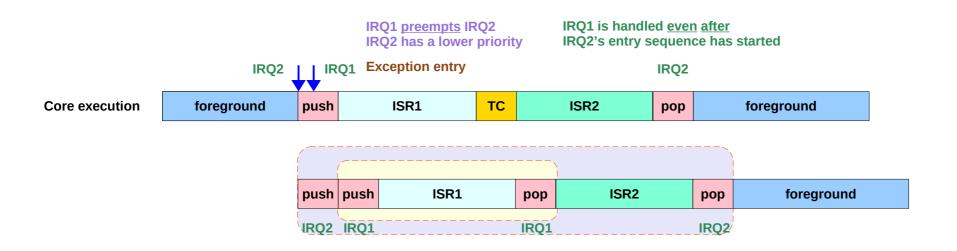

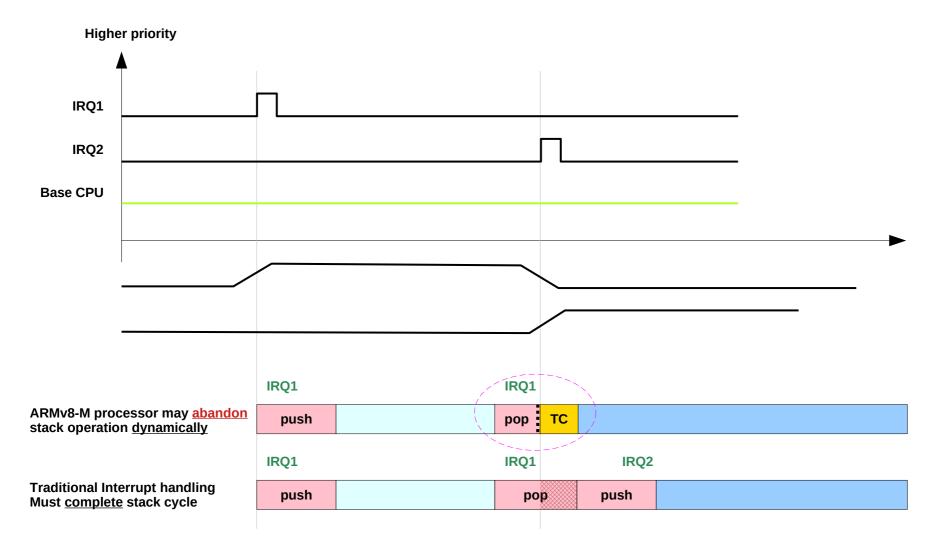

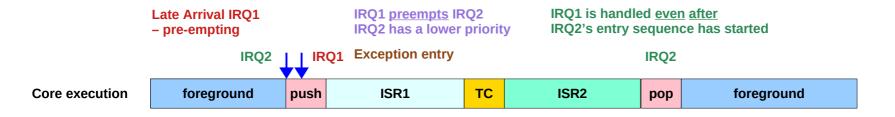

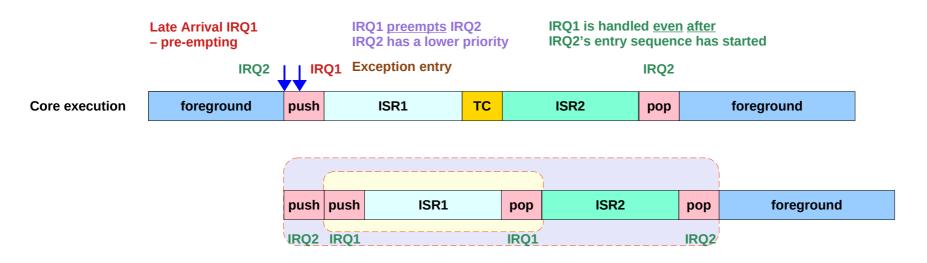

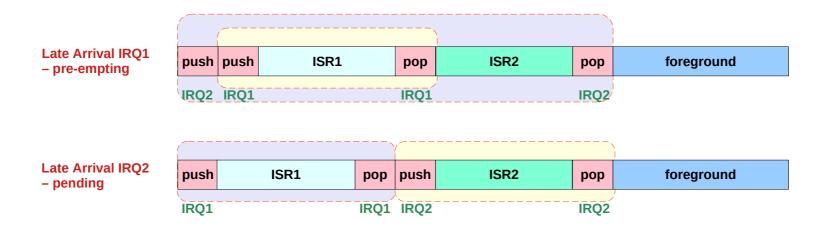

#### Late arrival A (1)

#### Late arrival A (2)

- a higher priority exception is handled before a lower priority exception

- just after the entry sequence of a lower priority exception has started

- the lower priority exception is handled <u>after</u> the higher priority exception is completed

#### Late arrival A (3)

- also, in the case of the late-arriving interrupt, the processor might execute its ISR after fewer cycles of interrupt latency.

- a lower priority IRQ2 interrupt causes the interrupt entry sequence to start.

- the interrupted context has its registers pushed onto the stack.

- while this is happening,

a higher priority IRQ1 interrupt occurs

- The processor still has to read the vector table to get the new vector

- but does <u>not</u> need to <u>restart</u> the <u>stack push</u>, so some cycles may be saved.

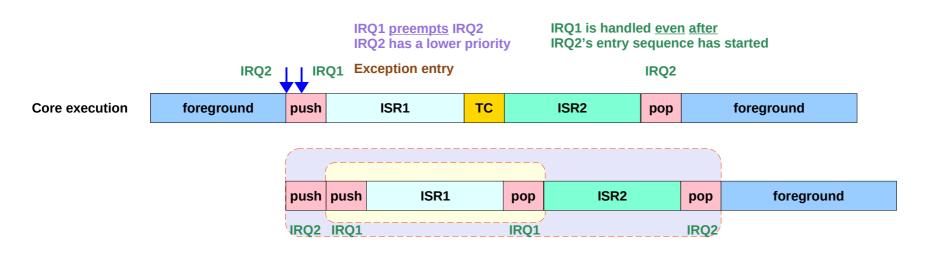

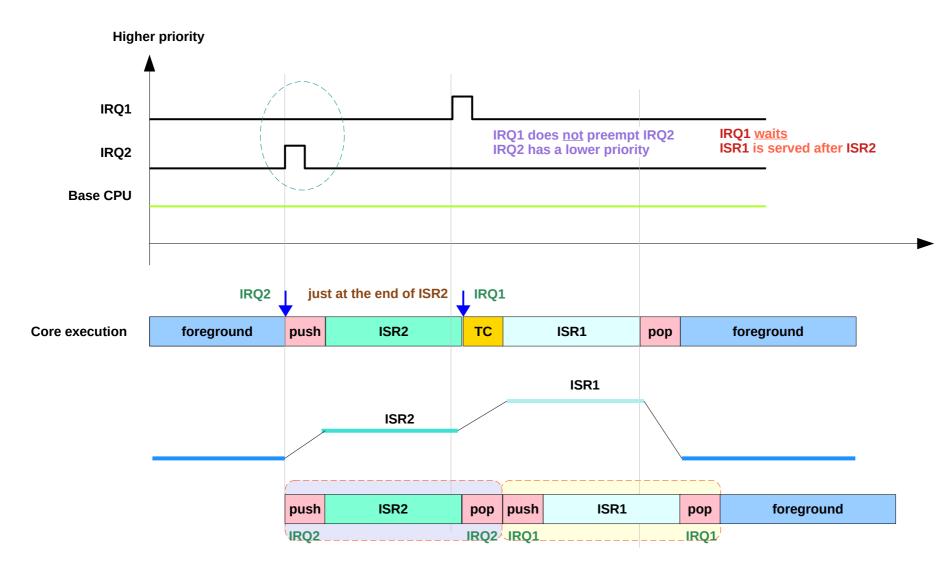

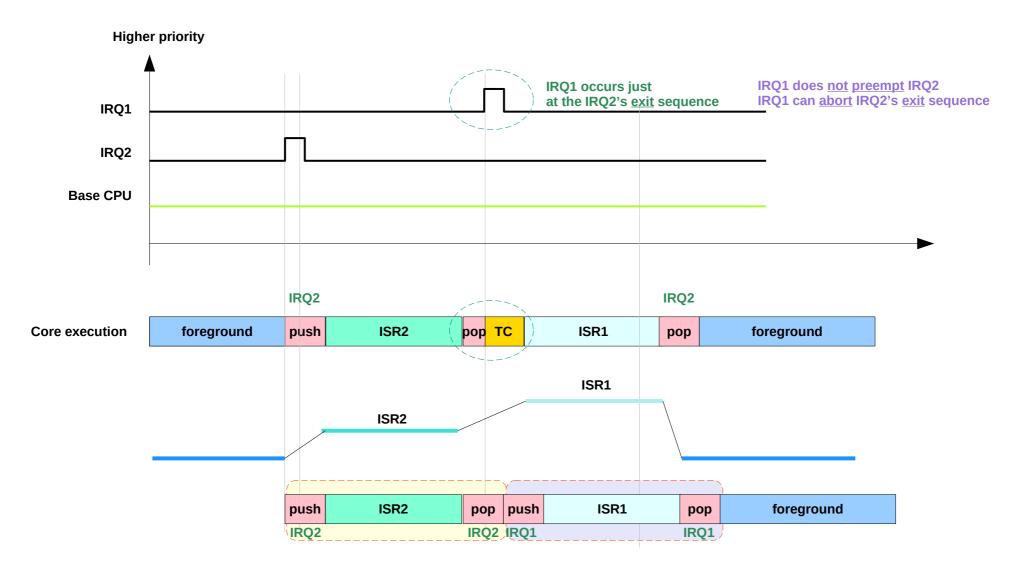

#### Late arrival B (1-1)

## Late arrival B (1-2)

#### Late arrival **B** (2)

- A similar case arises

if a new interrupt ISR2 arrives

just before the end of an ISR1,

- Priority (IRQ2) < Priority (IRQ1)</li>

- Priority (IRQ2) > any other pending or active ISR

- so that the newly detected interrupt immediately becomes the next interrupt to be handled in priority order.

- Again, the vector table needs to be <u>read</u> to access the new ISR1, but tail-chaining does <u>not require</u> any <u>stacking operation</u>

- The interrupt latency could be lower than normal.

#### Late arrival **C** (1)

#### Late arrival C (2)

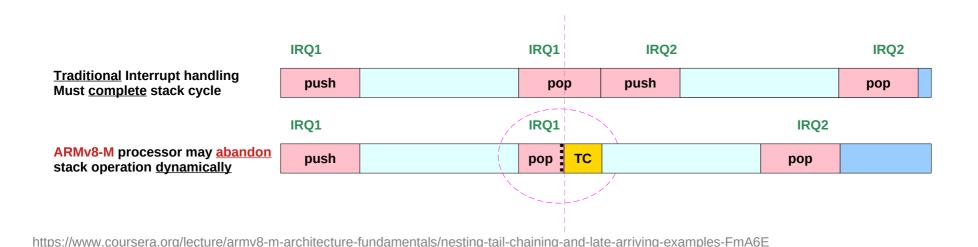

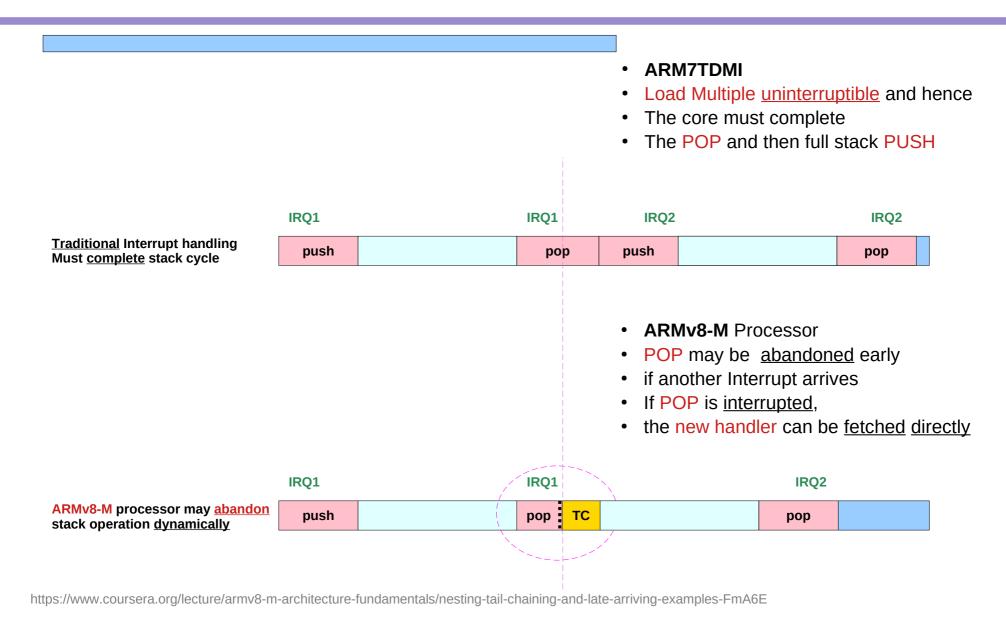

- In the case where the exception exit has already started, a similar situation arises.

- In the <u>traditional</u> model, the stack <u>pop</u> would have to <u>complete</u>, and then those same <u>registers</u> would need to be <u>pushed</u> again as part of the <u>new</u> <u>exception</u> handler.

In Cortex M,

the stack pop can simply be abandoned,

leaving the stack frame on the stack,

and only a tail-chain is then needed

to enter the new ISR.

#### Late arrival C (3)

#### Late arrival C (4)

## Nesting, Tail Chaining, and Late Arrival (2)

- The ARM-Architecture Reference Manual mentions three design options that can be implemented for **CortexM**.

- In the Instruction Set Attribute Register 2 (ID ISAR2), bits[11:8]:

- None supported.

This means the LDM and STM instructions are not interruptible. ARMv7-M reserved.

- LDM and STM instructions are restartable.

- LDM and STM instructions are continuable.

https://stackoverflow.com/questions/52924118/interrupted-load-multiple-store-multiple-on-cortexm

#### Late Arrival (1)

- A late-arriving interrupt is an interrupt which is recognized after the processor has started its exception entry procedure.

- If the late-arriving interrupt has <u>higher</u> pre-empting priority than the exception which the processor has already started to handle, then the <u>existing</u> stack push will <u>continue</u> but the <u>vector</u> fetch will be <u>re-started</u> using the vector for the <u>late-arriving</u> interrupt.

after starting an exception entry, other interrupts are requested

current **stack operation – utilized**

current **vector fetch** – **not used abandoned, restarted**

#### Late Arrival (2)

This <u>guarantees</u> that the interrupt with the <u>highest</u> <u>pre-empting</u> <u>priority</u> will be <u>serviced</u> <u>first</u>, but in some circumstances this results in some <u>wasted</u> cycles from the <u>original</u> <u>vector</u> <u>fetch</u> which was abandoned. after starting an exception entry, other interrupts are requested

current stack operation - utilized

current vector fetch - not used

abandoned,

restarted

→ wasted cycles

## Late Arrival (3)

If the late-arriving interrupt

has only equal priority to (or lower priority than)

the exception which the processor

has already started to handle,

then the late-arriving interrupt

will remain pending until

after the exception handler

for the current exception has run

#### Late Arrival (4)

• This is because the late-arriving behaviour is classed as a pre-empting behaviour, and is therefore dependent only upon the pre-empting priority levels of the interrupts and exceptions.

#### Late Arrival (5)

Because the stack push has already been initiated, the interrupt latency

(meaning the number of cycles between the arrival of the interrupt request and execution of the first instruction of its handler)

might be <u>less</u> than the <u>standard interrupt latency</u> for the particular processor and system.

#### **Standard Stack Operations**

## Late Arrival (6)

- Some (but not all) Cortex-M processors provide an implementation-time option for the chip designer to specify a minimum value for the interrupt latency, reducing or removing the uncertainty in interrupt latency by adding stall cycles in such cases.

- Documentation of the specific chip should provide details of this setting, if applicable.

Interrupt latency > min value

min value

: set at the implementation time

add stall cycles to small interrupt latency to meet the min value

## Single copy atomicity in ARM (1)

- a read or write operation is single-copy atomic if the following conditions are both true:

- after any number of write operations to a memory location, the value of the memory location is the value written by one of the write operations.

- It is impossible for part of the value of the memory location to come from one write operation and another part of the value to come from a different write operation

https://stackoverflow.com/questions/24010989/arm-single-copy-atomicity

#### Single copy atomicity in ARM (2)

- When a read operation and a write operation are made to the same memory location, the value obtained by the read operation is one of:

- the value of the memory location before the write operation

- the value of the memory location after the write operation.

- It is <u>never</u> the case that

the value of the **read** operation is

partly the value of the memory location

<u>before</u> the **write** operation

and partly the value of the memory location

<u>after</u> the **write** operation.

https://stackoverflow.com/questions/24010989/arm-single-copy-atomicity

#### Single copy atomicity in ARM (3)

So your understanding is right - the defining point of a single-copy atomic operation is that at any given time you can only ever see either all of it, or none of it.

.

There is a case in v7 whereby (if I'm interpreting it right)

two normally single-copy atomic stores that occur to the

same location at the same time but with different sizes

break any guarantee of atomicity, so in theory you could

observe some unexpected mix of bytes there - this looks

to have been removed in v8.

https://stackoverflow.com/questions/24010989/arm-single-copy-atomicity

#### Interruptible LDM, STM (1)

- the load multiple (LDM) instructions are explicitly <u>not atomic</u>.

- section A3.5.3 of the ARM V7C architecture reference manual.

- LDM, LDC, LDC2, LDRD, STM, STC, STC2, STRD, PUSH, POP, RFE, SRS, VLDM, VLDR, VSTM, and VSTR instructions

- are <u>executed</u> as a <u>sequence</u> of word-aligned <u>word accesses</u>.

- <u>each</u> 32-bit word access is guaranteed to be single-copy atomic.

- the architecture does <u>not require</u> subsequences of <u>two or more</u> word accesses from the sequence to be <u>single-copy</u> atomic.

#### Interruptible LDM, STM (2)

- the LDM/STM instructions

can be aborted by an interrupt

and restarted from the beginning on interrupt return

- LDM and STM instructions

can always be interrupted by a data abort,

so they're non atomic in that sense.

- Otherwise, the ARMv7-A architecture does its best to help you out.

- for interrupts, they can <u>only</u> be interrupted

- if low interrupt latency is enabled,

- AND normal memory is being accessed.

- So at the very least, you won't get repeated accesses to device memory.

- You <u>don't</u> want to <u>do anything</u> that expects <u>atomic read/writes</u> of normal memory though.

#### Interruptible LDM, STM (3)

- On v7-M, LDM and STM can be interrupted at any time

- see section B1.5.10 of the ARMv7-M Architecture Reference Manual

- It's implementation defined

- whether or not the instruction is restarted from the beginning of the list of loads/stores,

- or whether it's restarted from where it left off.

- •

- •

- •

#### Interruptible LDM, STM (4)

- As the ARM says:

- The ARMv7-M architecture supports

- · continuation of, or

- restarting from the beginning,

- an abandoned LDM or STM instruction as outlined below.

- Where an LDM or STM is abandoned and restarted (ICI bits are not supported),

- the instructions should not be used with volatile memory.

- In other words, <u>don't rely on LDM</u> or <u>STM</u> being atomic if you're trying to write <u>portable code</u>.

## Interruptible LDM, STM (6)

- Application Program Status Register (APSR)

- The **APSR** contains the current state of the <u>condition</u> <u>flags</u> from <u>previous instruction executions</u>.

- Interrupt Program Status Register (IPSR)

- The IPSR contains the exception type number of the current Interrupt Service Routine (ISR)

- Execution Program Status Register (EPSR)

- The EPSR contains

- the thumb state bit, and

- the execution state bits

- for either the:

- **If-Then** (IT) instruction

- Interruptible-Continuable Instruction (ICI) field for an interrupted load multiple or store multiple instruction.

https://developer.arm.com/documentation/dui0552/a/the-cortex-m3-processor/programmers-model/core-registers

## If-Then (IT) block

- The If-Then (IT) block contains up to <u>four</u> instructions following an IT instruction

- each instruction in the block is conditional.

- the conditions for the instructions are

- either all the same, or Then

- some can be the inverse of others.

ITTET EQ

ADD r0,r0,r0

ADD r1,r0,r0

ADD r2,r0,r0

ADD r3,r0,r0

IT block size = 4

https://developer.arm.com/documentation/dui0552/a/the-cortex-m3-processor/programmers-model/core-registers

## If-Then (IT) block examples

First note that most instruction can specify a condition code in ARM instruction, <u>not</u> in Thumb.

With **IT** instruction, you can specify condition code for <u>up to 4 instructions</u>. For each instruction, you specify if it's part of the **If** (**T**) or **Else** (**E**).

#### For example:

```

ITTET EQ Then, Then, Else, Then \rightarrow EQ, EQ, NE, EQ ADD r0,r0,r0 ADD r1,r0,r0 ADD r2,r0,r0 ADD r3,r0,r0

```

Will actually translate to:

```

ADDEQ r0,r0,r0 (Always if for 1st one)

ADDEQ r1,r0,r0 (T for 2nd one)

ADDNE r2,r0,r0 (E for 3rd one)

ADDEQ r3,r0,r0 (T for 4th one)

```

https://stackoverflow.com/questions/36558926/what-does-the-arm7-it-if-then-instruction-really-do

## **Condition Code Encoding**

| Code | Suffix | Flags                       | Meaning                 |

|------|--------|-----------------------------|-------------------------|

| 0000 | EQ     | Z set                       | equal                   |

| 0001 | NE     | Z clear                     | not equal               |

| 0010 | CS     | C set                       | unsigned higher or same |

| 0011 | CC     | C clear                     | unsigned lower          |

| 0100 | MI     | N set                       | negative                |

| 0101 | PL     | N clear                     | positive or zero        |

| 0110 | VS     | V set                       | overflow                |

| 0111 | VC     | V clear                     | no overflow             |

| 1000 | HI     | C set and Z clear           | unsigned higher         |

| 1001 | LS     | C clear or Z set            | unsigned lower or same  |

| 1010 | GE     | N equals V                  | greater or equal        |

| 1011 | LT     | N not equal to V            | less than               |

| 1100 | GT     | Z clear AND (N equals V)    | greater than            |

| 1101 | LE     | Z set OR (N not equal to V) | less than or equal      |

| 1110 | AL     | (ignored)                   | always                  |

| 1111 | rsvd   |                             |                         |

| ,    |        | D1 D2 D2 D4                 |                         |

→ P1, P2, P3, P4

base condition

http://www.csbio.unc.edu/mcmillan/Media/arm-instructionset.pdf

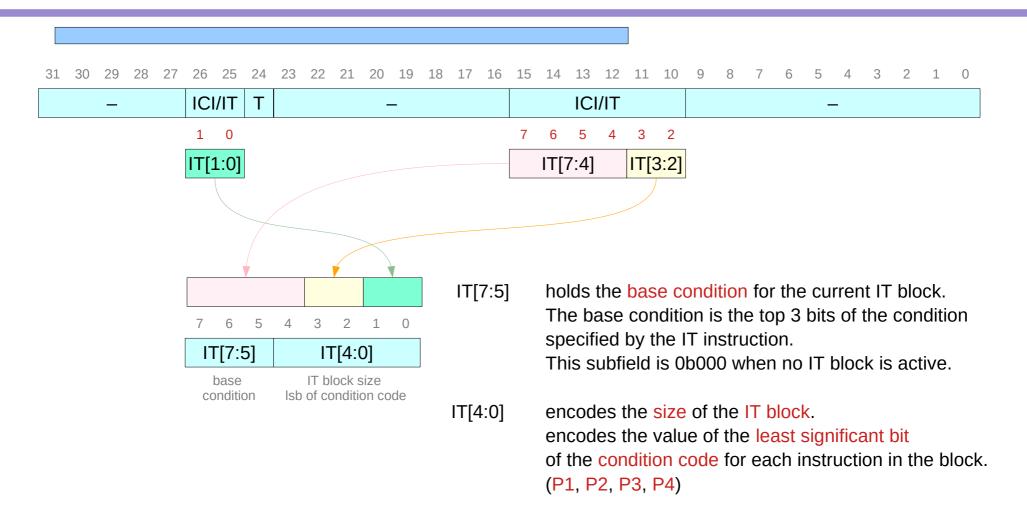

## ESPR fields for IT block (1)

## ESPR fields for IT block (2)

IT[4:0] encodes the size of the IT block.

This is the number of instructions that are to be conditionally executed.

The size of the block is implied by the position of the least significant 1 in this field

encodes the value of the least significant bit of the condition code for each instruction in the block. (P1, P2, P3, P4)

ADD r0,r0,r0 ADD r1,r0,r0 ADD r2,r0,r0 ADD r3,r0,r0

IT block size = 4

| [4] | [3]            | [2]   | [1]                                    | [0]                                            |                                                   |

|-----|----------------|-------|----------------------------------------|------------------------------------------------|---------------------------------------------------|

| P1  | P2             | P3    | P4                                     | 1                                              | Entry point for 4-instruction IT block            |

| P1  | P2             | Р3    | 1                                      | 0                                              | Entry point for 3-instruction IT block            |

| P1  | P2             | 1     | 0                                      | 0                                              | Entry point for 2-instruction IT block            |

| P1  | 1              | 0     | 0                                      | 0                                              | Entry point for 1-instruction IT block            |

| 0   | 0              | 0     | 0                                      | 0                                              | Normal execution, not in an IT block              |

|     | P1<br>P1<br>P1 | P1 P2 | P1 P2 P3<br>P1 P2 P3<br>P1 P2 <b>1</b> | P1 P2 P3 P4 P1 P2 P3 <b>1</b> P1 P2 <b>1</b> 0 | P1 P2 P3 P4 1 P1 P2 P3 1 0 P1 P2 1 0 0 P1 1 0 0 0 |

## ESPR fields for IT block (3)

|           | 7 6    | 5 4 | 4 3     | 2 1 | 0   |                                       |

|-----------|--------|-----|---------|-----|-----|---------------------------------------|

|           | IT[7:5 | 5]  | IT[4:0] |     |     |                                       |

|           |        |     |         |     |     |                                       |

| [7:5]     | [4]    | [3] | [2]     | [1] | [0] |                                       |

| cond_base | P1     | P2  | P3      | P4  | 1   | Entry point for 4-instruction IT bloc |

| cond_base | P1     | P2  | P3      | 1   | 0   | Entry point for 3-instruction IT bloc |

| cond_base | P1     | P2  | 1       | 0   | 0   | Entry point for 2-instruction IT bloc |

| cond_base | P1     | 1   | 0       | 0   | 0   | Entry point for 1-instruction IT bloc |

| 000       | 0      | 0   | 0       | 0   | 0   | Normal execution, not in an IT bloc   |

| ITTET EQ     |

|--------------|

| ADD r0,r0,r0 |

| ADD r1,r0,r0 |

| ADD r2,r0,r0 |

| ADD r3,r0,r0 |

ADDEQ r0,r0,r0 (Always if for 1st one)

ADDEQ r1,r0,r0 (T for 2nd one)

ADDNE r2,r0,r0 (E for 3rd one)

ADDEQ r3,r0,r0 (T for 4th one)

EQ condition code = 0000 NE condition code = 0001 base code = 000 P1=0, P2=0, P3=1, P4=0

TTET

IT[7:5] = 000, IT[4:0] = 00101

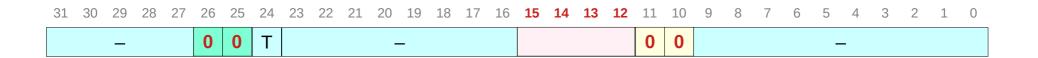

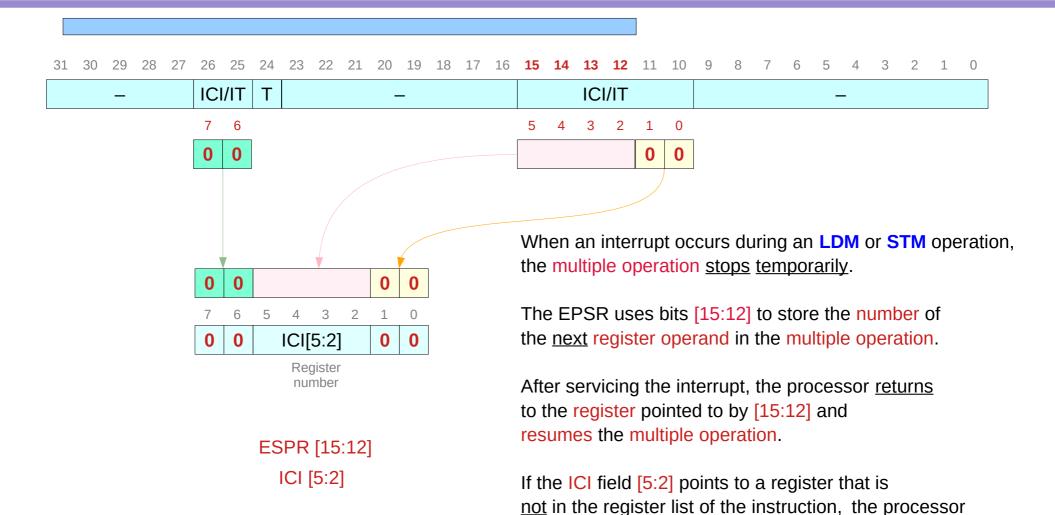

## Interruptible-Continuable Instructions (ICI)

- When an interrupt occurs during the execution of an LDM, STM, PUSH, or POP instruction, the processor:

- stops the load multiple or store multiple instruction operation temporarily

- stores the next register operand in the multiple operation to EPSR bits[15:12].

- after servicing the interrupt, the processor:

- returns to the register pointed to by EPSR bits[15:12]

- resumes execution of the multiple load or store instruction.

• When the **EPSR** holds **ICI** execution state bits[26:25,11:10] are zero.

https://developer.arm.com/documentation/dui0552/a/the-cortex-m3-processor/programmers-model/core-registers

## ESPR fields for ICI bits (1)

https://developer.arm.com/documentation/ddi0337/e/ch02s03s02

continues with the next register in the list, if any.

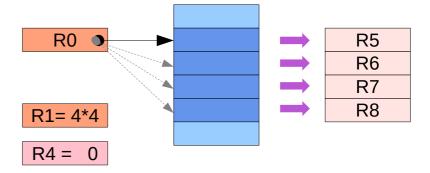

## LDM / STM examples (1)

allowing several values to be loaded or stored

For example, **LDMIA** instruction allows loading into multiple registers (R5, R6, R7, R8) starting at an address named in another register (R0).

Consider the example of adding the integers of an array. **LDMIA** can be used to processes four integers with each iteration of the loop.

In this way, fewer instructions can be used, at the expense of more complexity.

**LDMIA** R0!, { R5-R8 }

http://www.cburch.com/books/arm/

## LDM / STM examples (2)

If the exclamation mark! following R0 is omitted, then the address register R0 is <u>not</u> altered R0 would continue pointing to the first integer in the array.

we want R0 to change so that it is pointing to the next four integers for the next iteration, the exclamation point should be included

### **LDMIA** R0!, { R5-R8 }

# equivalent instructions <u>without</u>! **pre-indexed**

http://www.cburch.com/books/arm/

# equivalent instructions with ! post-indexed

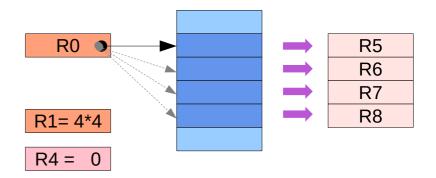

## LDM / STM examples (3)

#### **LDMIA** R0!, { R5-R8 }

equivalent instructions with ! post-indexed

```

LDR R5, =[R0], #4

LDR R6, =[R0], #4

LDR R7, =[R0], #4

LDR R8, =[R0], #4

```

the multiple operation

```

ESPR [15:12] (=ICI [5:2])

```

could be R5, R6, R7, R8 In this example

https://developer.arm.com/documentation/ddi0337/e/ch02s03s02

Assume an interrupt happens in the middle of LDR R6 = [R0], #4 operation

When an interrupt occurs during an **LDM** or **STM** operation, the multiple operation stops temporarily.

```

LDR R5 = [R0], #4

LDR R6 = [R0], #4

LDR R7 = [R0], #4 ; the stopped operation

LDR R8 = [R0], #4

```

The EPSR uses bits [15:12] to store the number of the <u>next</u> register operand in the multiple operation.

R6

After servicing the interrupt, the processor <u>returns</u> to the <u>register</u> pointed to by [15:12] and <u>resumes</u> the <u>multiple</u> operation.

```

LDR R5 =[R0], #4

LDR R6 =[R0], #4

LDR R7 =[R0], #4 ; resume the stopped op

LDR R8 =[R0], #4

```

### Thumb state

- The Cortex-M3 processor only supports execution of instructions in Thumb state.

- The following can clear the **T** bit to **0**:

- instructions BLX, BX and POP{PC}

- restoration from the stacked xPSR value on an exception return

- bit[0] of the vector value on an exception entry or reset.

- Attempting to execute instructions when the T bit is 0 results in a fault or lockup. See Lockup for more information.

https://developer.arm.com/documentation/dui0552/a/the-cortex-m3-processor/programmers-model/core-registers and the cortex-m3-processor/programmers-model/core-registers and the cortex-m3-processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/processor/process

### Current state bit in CPSR

- The CPSR register holds

- processor mode bits (user or exception flag)

- · interrupt mask bits

- condition codes and

- Thumb status bit

- The Thumb status bit (T) <u>indicates</u> the processor's <u>current state</u>:

- 0 for ARM state (default)

- · 1 for Thumb.

- Although other <u>bits</u> in the <u>CPSR</u> may be <u>modified</u> in software, it's <u>dangerous</u> to <u>write</u> to <u>T</u> directly;

- the results of an improper state change are *unpredictable*.

N Negative flag

**Z** Zero flag

C Carry flag

**V** Overflow flag

To <u>disable</u> Interrupt (**IRQ**), set **I**To <u>disable</u> Fast Interrupt (**FIQ**), set **F**

**USR** User mode

FIQ Fast Interrupt mode

**SVC** Supervisor mode

**ABT** Abort mode

**UND** Undefined mode

SYS System mode

https://www.embedded.com/introduction-to-arm-thumb/

### ESPR T-bit field

Field Name

Definition

[24] T

The T-bit can be cleared using an interworking instruction where bit [0] of the written PC is 0.

It can also be cleared by unstacking from an exception where the stacked T bit is 0.

Executing an instruction while the T bit is clear causes an INVSTATE exception.

## Interruptible-Continuable Instruction (ICI) bits

| Field                | Name | Definition                                                                                                                                                     |

|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:27]              | -    | Reserved.                                                                                                                                                      |

| [26:25], [15:10] ICI |      | Interruptible-continuable instruction bits.                                                                                                                    |

|                      |      | When an interrupt occurs during an LDM or STM operation, the multiple operation stops temporarily.                                                             |

|                      |      | The EPSR uses bits [15:12] to store the number of the next register operand in the multiple operation.                                                         |

|                      |      | After servicing the interrupt, the processor returns to the register pointed to by [15:12] and resumes the multiple operation.                                 |

|                      |      | If the ICI field points to a register that is not in the register list of the instruction, the processor continues with the next register in the list, if any. |

## If-Then (IT) block

| Field         | Name   | Definition                                                                                                                                                                                                                                                            |

|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [26:25], [15: | 10] IT | If-Then bits. These are the execution state bits of the If-Then instruction. They contain the number of instructions in the if-then block and the conditions for their execution.                                                                                     |

| [24]          | Т      | The T-bit can be cleared using an interworking instruction where bit [0] of the written PC is 0. It can also be cleared by unstacking from an exception where the stacked T bit is 0. Executing an instruction while the T bit is clear causes an INVSTATE exception. |

| [23:16]       | -      | Reserved.                                                                                                                                                                                                                                                             |

| [9:0] -       |        | Reserved.                                                                                                                                                                                                                                                             |

## Interruptible LDM, STM (5)

- If an STM or LDM instruction is interrupted,

EPSR is set to indicate the point from which the execution can continue, and then exception entry is triggered.

- the <u>stacked</u> PSR value that contains this information, just as it contains the <u>Thumb</u> bit from the interrupted code.

- If your new context has <u>zero</u> in the <u>ISI</u> <u>bits</u> of the <u>stacked</u> <u>PSR</u>, you should not see a usage fault exception for the reasons you give.

## Interruptible LDM, STM (7)

- The ICI/IT field is part of EPSR, not IPSR, not that it makes a huge amount of difference if you're interacting with xPSR.

- If an STM or LDM instruction is interrupted, EPSR is

- <u>set</u> to indicate the <u>point</u>

from which the execution can <u>continue</u>, and then

- exception entry is triggered.

- It is therefore the stacked PSR value that contains this information, just as it contains the Thumb bit from the interrupted code.

- If your new context has <u>zero</u>

in the ISI bits of the <u>stacked PSR</u>,

you should <u>not</u> see a usage fault exception for the reasons

you give. (In the absence of any code, I can't really be

more specific than this.)

## Interruptible LDM, STM (8)

- If LDM and STM are implemented as restartable or continuable, then no, the stack will not be corrupted by this process. (That would be a nightmare!)

- If LDM and STM are restartable

then the stack pointer is simply reset to the value

it had at the start of the LDM/STM

and the instruction is executed anew;

- if they are continuable then the stack pointer is not modified but a partial STM/LDM is performed to complete the instruction.

## Interruptible LDM, STM (9)

• You don't mention exactly how you're achieving a context switch, but I assume you are manually pushing r4-r11 to the process stack, then saving the PSP somewhere and updating it to point to the new context on a different stack, before popping r4-r11 and triggering an exception return - that's certainly the usual way to go about it.

#### References

- [1] http://wiki.osdev.org/ARM\_RaspberryPi\_Tutorial\_C

- [2] http://blog.bobuhiro11.net/2014/01-13-baremetal.html

- [3] http://www.valvers.com/open-software/raspberry-pi/

- [4] https://www.cl.cam.ac.uk/projects/raspberrypi/tutorials/os/downloads.html