# Pipelined Architecture (2A)

| Copyright (c) 2014 - 2018 Young W. Lim.                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

| Please send corrections (or suggestions) to youngwlim@hotmail.com.                                                                                                                                                                                                                                                                                                              |

| This document was produced by using LibreOffice.                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

#### Based on

ARM System-on-Chip Architecture, 2<sup>nd</sup> ed, Steve Furber

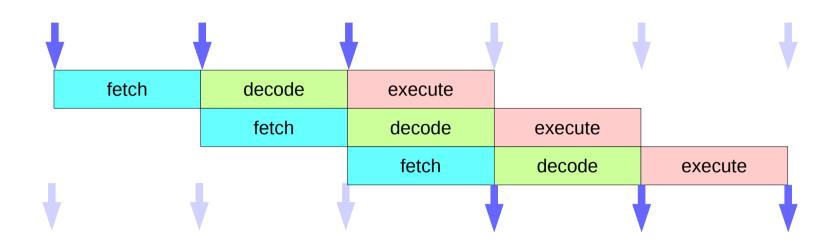

#### 3-stage

fetch

- the instruction is fetched from memory

- it is placed in the instruction pipeline

decode

- · the instruction is decoded

- next cycle control signal is prepared

- the decode logic but not the datapath is dedicated

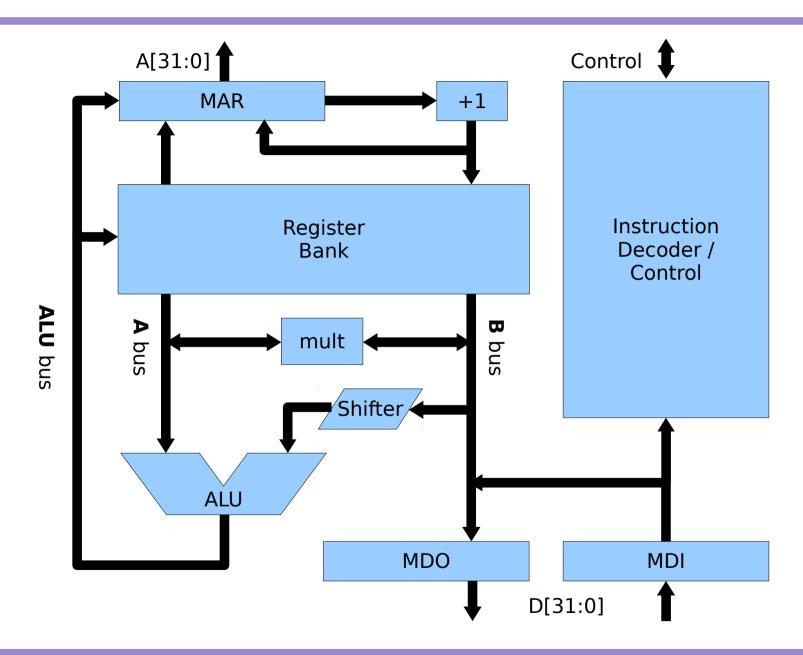

execute

- · the datapath is dedicated

- <u>reading</u> the <u>register</u> bank

- · shifting an operand

- performing <u>ALU</u> operations

- writing back the result into the register bank

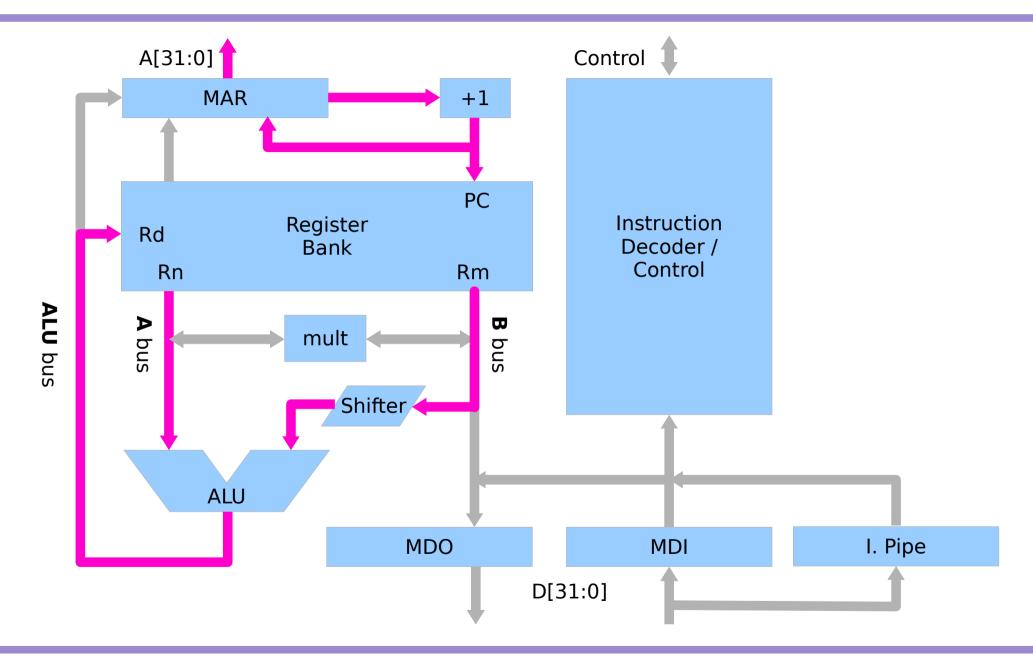

## 3 stage pipeline – single cycle

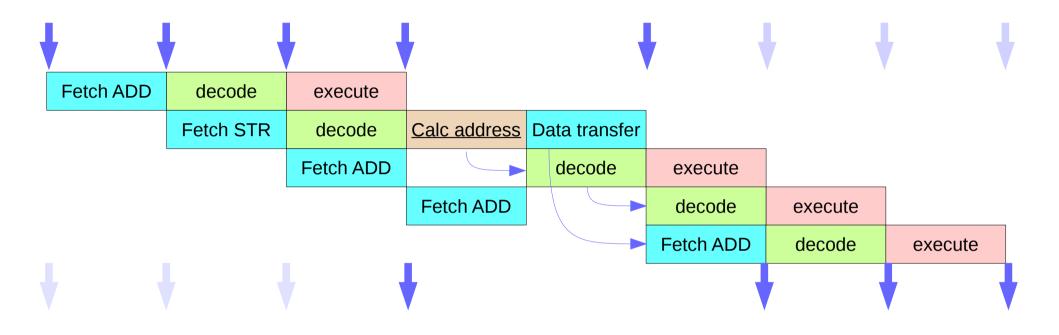

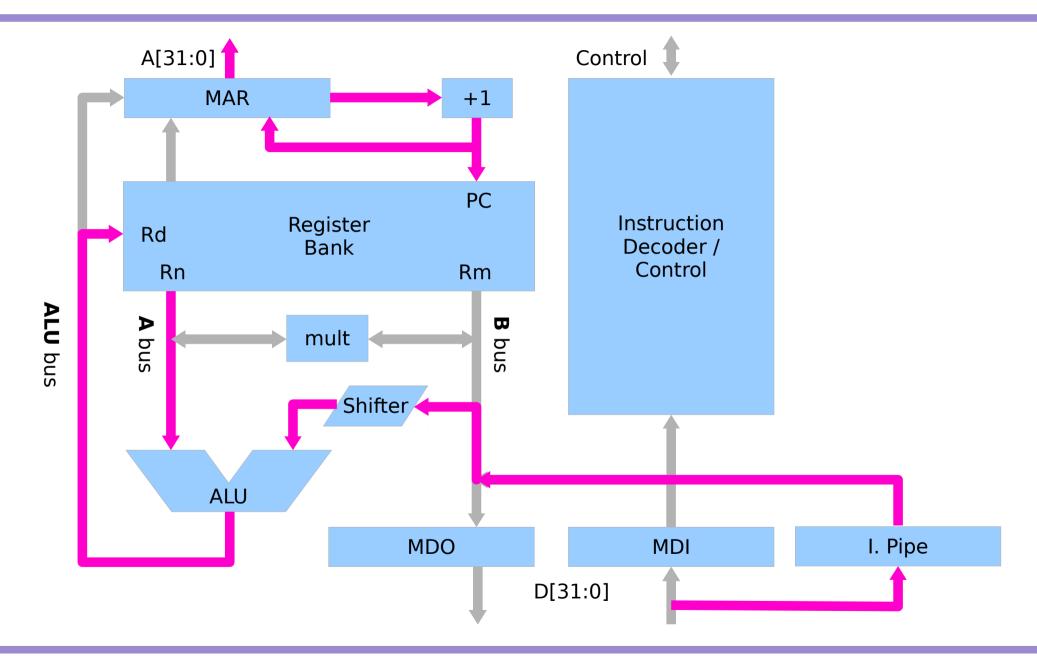

## 3-stage pipeline – multi-cycle

the decode logic is involved in all the <u>decode</u> cycle the <u>address calculation</u>

the datapath is involved in all the execute cycle the address calculation the data transfer

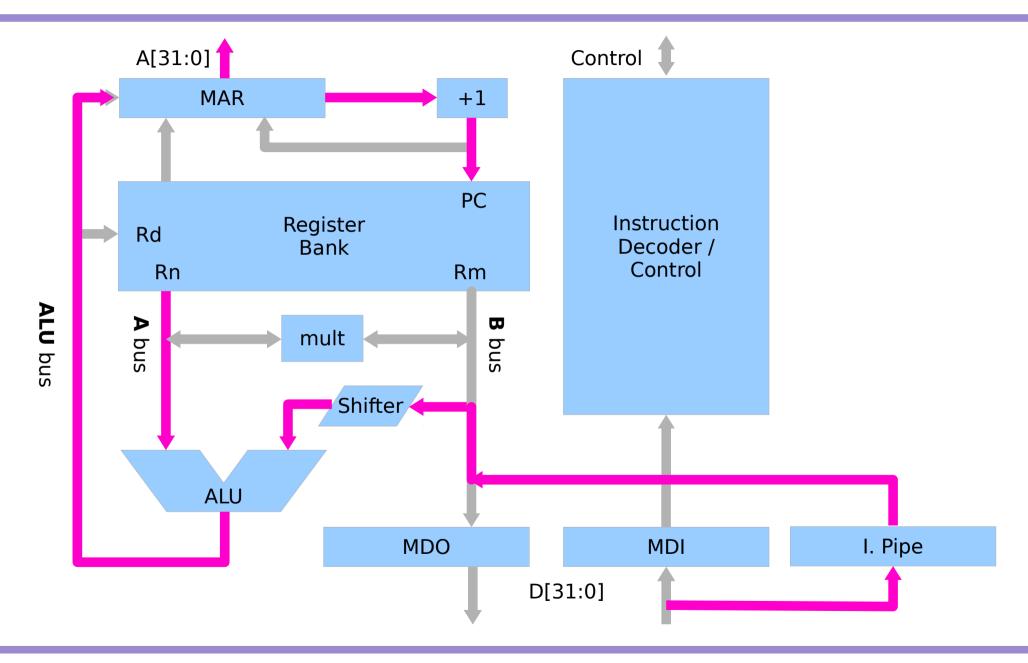

## 3-stage pipeline – multi-cycle

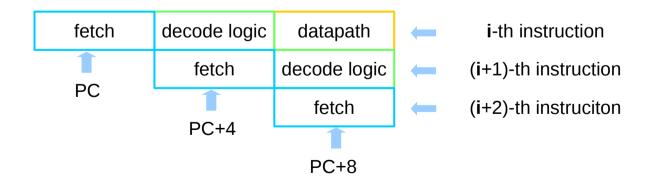

decode logic

datapath

decode

execute

Calc address

Calc address

Data transfer

## 3-stage pipeline – multi-cycle

### 3-stage Pipeline

## **Data Processing Instructions**

| 31 | 30   | 29 | 28 | 27    | 26 | 25 | 24     | 23  | 22  | 21 | 20   | 19   | 18 | 17 | 16 | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7         | 6     | 5    | 4       | 3 | 2 | 1 | 0 |

|----|------|----|----|-------|----|----|--------|-----|-----|----|------|------|----|----|----|--------|----|----|----|----|----|---|---|-----------|-------|------|---------|---|---|---|---|

|    | СО   | nd |    | 0     | 0  | #  | opcode |     |     | S  | S Rn |      |    |    | Rd |        |    |    |    |    |    |   | 0 | Operand 2 |       |      |         |   |   |   |   |

|    |      |    |    |       |    |    |        |     |     |    |      |      |    |    |    |        |    |    |    |    |    |   |   |           |       |      |         |   |   |   |   |

|    |      |    |    |       |    |    |        |     |     |    |      |      |    |    |    |        |    |    |    |    |    |   |   |           |       |      |         |   |   |   |   |

| 31 | 30   | 29 | 28 | 27    | 26 | 25 | 24     | 23  | 22  | 21 | 20   | 19   | 18 | 17 | 16 | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7         | 6     | 5    | 4       | 3 | 2 | 1 | 0 |

|    | СО   | nd |    | 0 0 1 |    |    | opcode |     |     |    | S    | S Rn |    |    |    | Rd     |    |    |    | #r | ot |   |   | 8         | 3-bit | t im | mediate |   |   |   |   |

|    |      |    |    |       |    |    | •      |     |     |    |      |      |    |    |    | •      |    |    |    |    |    |   |   |           |       |      |         |   |   |   |   |

|    |      |    |    |       |    |    |        |     |     |    |      |      |    |    |    |        |    |    |    |    |    |   |   |           |       |      |         |   |   |   |   |

| 31 | 30   | 29 | 28 | 27    | 26 | 25 | 24     | 23  | 22  | 21 | 20   | 19   | 18 | 17 | 16 | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7         | 6     | 5    | 4       | 3 | 2 | 1 | 0 |

|    | cond |    |    | 0     | 0  | 0  | opcode |     | S   | Rn |      |      | Rd |    |    | #shift |    |    |    |    | Sh |   |   | ) Rm      |       |      |         |   |   |   |   |

|    |      |    |    |       |    |    |        |     |     |    |      |      |    |    |    |        |    |    |    |    |    |   |   |           |       |      |         |   |   |   |   |

|    |      |    |    |       |    |    |        |     |     |    |      |      |    |    |    |        |    |    |    |    |    |   |   |           |       |      |         |   |   |   |   |

| 31 | 30   | 29 | 28 | 27    | 26 | 25 | 24     | 23  | 22  | 21 | 20   | 19   | 18 | 17 | 16 | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7         | 6     | 5    | 4       | 3 | 2 | 1 | 0 |

|    | cond |    |    | 0     | 0  | 0  |        | opc | ode | ļ  | S    |      | R  | n  |    |        | R  | d  |    |    | R  | S |   | 0         | S     | h    | 1       |   | R | m |   |

## Register-Register Operations

## Register-Immediate Operations

## Single word and unsigned byte data transfer instructions

| 31 | 30   | 29   | 28 | 27 | 26    | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|----|------|------|----|----|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|-----|-----|---|---|---|---|---|

|    | СО   | cond |    | 0  | 1 #   |    | Р  | U  | В  | W  | L  |    | R  | n  |    |    | R  | d  |    |    |    |   |   |   | off | set |   |   |   |   |   |

|    |      |      |    |    | ,     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |     |     |   |   |   |   |   |

|    |      |      |    |    |       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |     |     |   |   |   |   |   |

|    |      |      |    |    |       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |     |     |   |   |   |   |   |

| 31 | 30   | 29   | 28 | 27 | 26    | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|    | cond |      |    |    | 0 1 0 |    | Р  | U  | В  | W  | L  |    | R  | n  |    |    | R  | :d |    |    |    |   |   |   | off | set |   |   |   |   |   |

|    |      |      |    |    |       |    |    |    |    |    |    | l  |    |    |    |    |    |    |    |    |    |   |   |   |     |     |   |   |   |   |   |

|    |      |      |    |    |       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |     |     |   |   |   |   |   |

| 31 | 30   | 29   | 28 | 27 | 26    | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|    | cond |      |    | 0  | 1     | 1  | Р  | U  | В  | W  | ı  |    | R  | n  |    |    | R  | d  |    |    |    | R |   |   | S   | h   | 0 |   | F | ? |   |

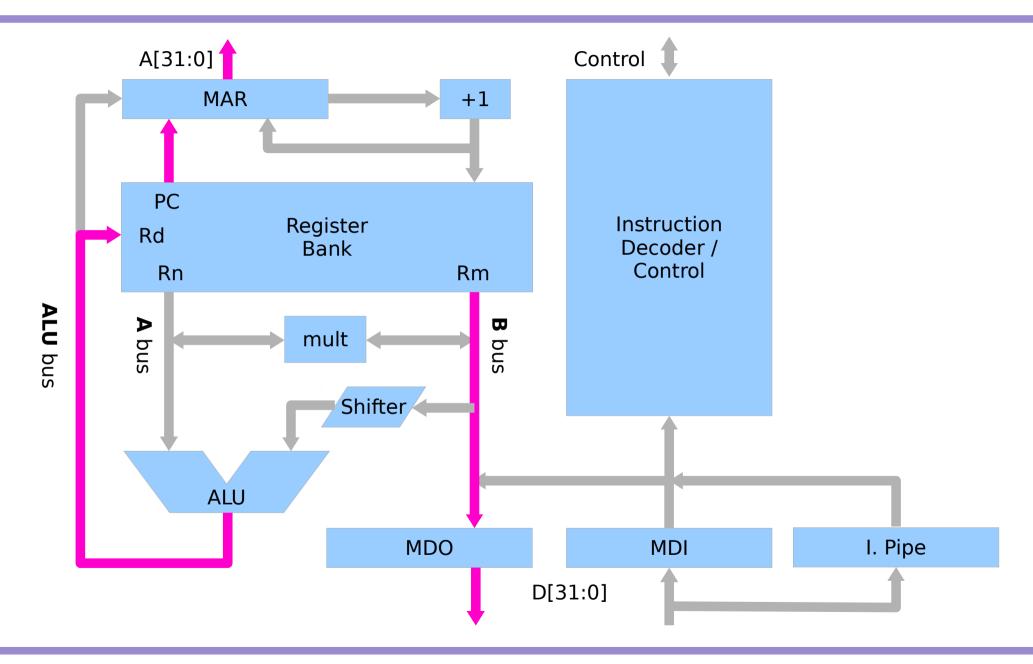

## STR - 1<sup>st</sup> Cycle

## STR - 2<sup>nd</sup> Cycle

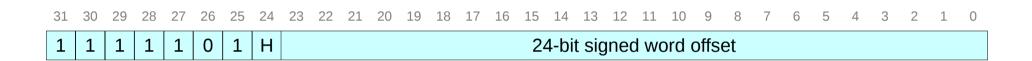

#### Branch and Branch with Link (B, BL)

#### Branch, Branch with Link and eXchange (BX, BLX)

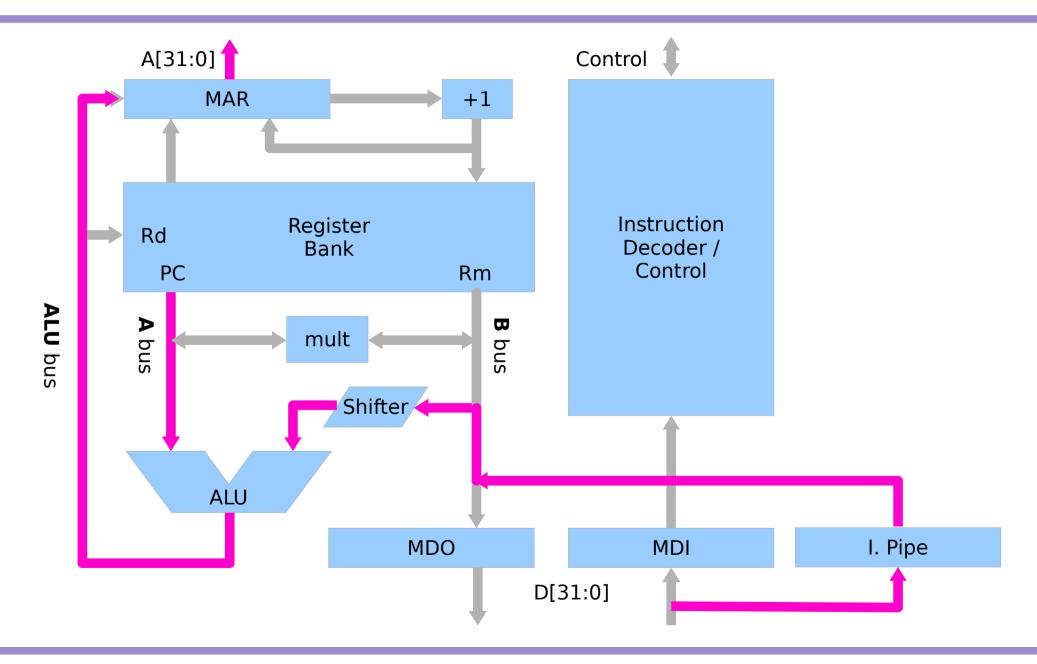

## B - 1<sup>st</sup> Cycle

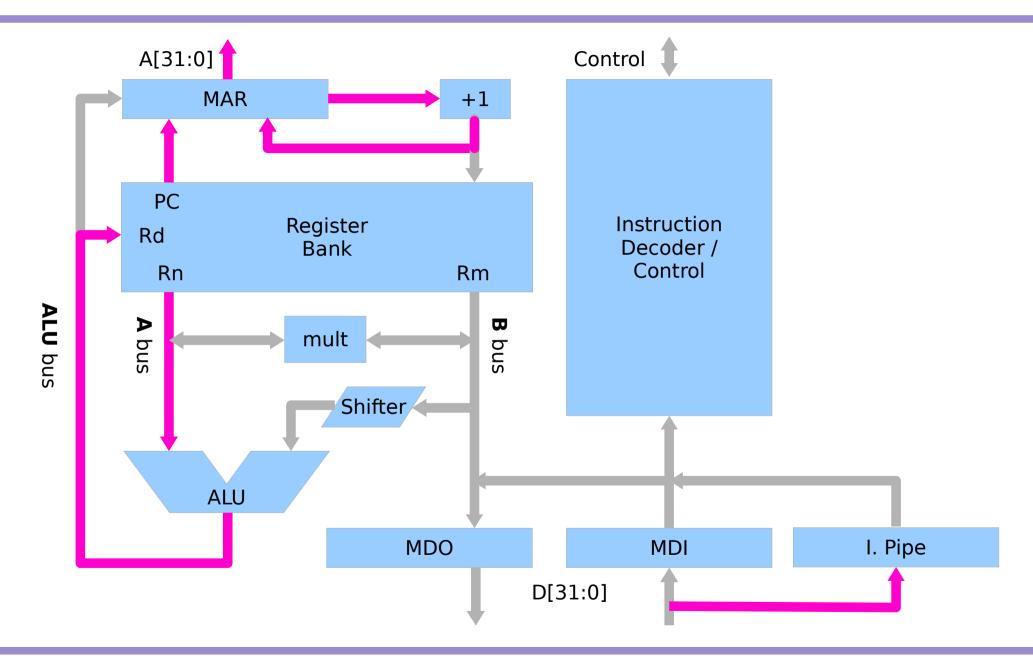

## B - 2<sup>nd</sup> Cycle

#### **ARM Instruction Set**

The load-store architecture

3-address data processing instructions

(2 source registers + 1 destination register)

Conditionally executes every instruction

Multiple data transfer instruction

Single cycle execution of shift and ALU operations

Open instruction set for coprocessors

A very dense 16-bit compressed instruction set (Thumb)

## **ARM Exception Handling**

C R R RRRRRR RR R R R R RR R R R R Ν Ζ V R R R|R|R|R R R

#### References

- [1] ftp://ftp.geoinfo.tuwien.ac.at/navratil/HaskellTutorial.pdf

- [2] https://www.umiacs.umd.edu/~hal/docs/daume02yaht.pdf